7.1.4 CLA Delay

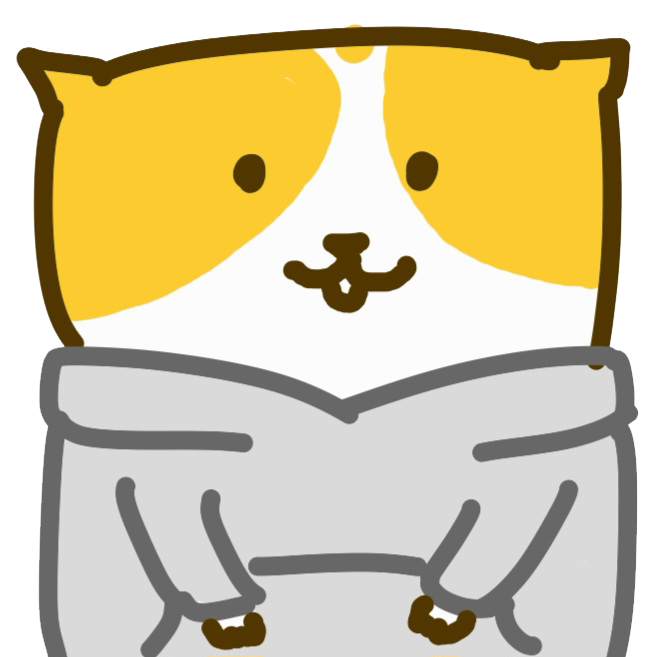

CLA의 Delay의 계산 결과를 보면 위와 같이 계산되는 것을 확인할 수 있다. 보면 알겠지만 원래 가산기 회로에 비해서 속도가 점차 빨라지는 것을 확인할 수 있다. 이것은 이미 기존에 값을 게산해 두었기 때문에 속도가 빨라진 것을 확인할 수 있다.

7.1.6 가감산기

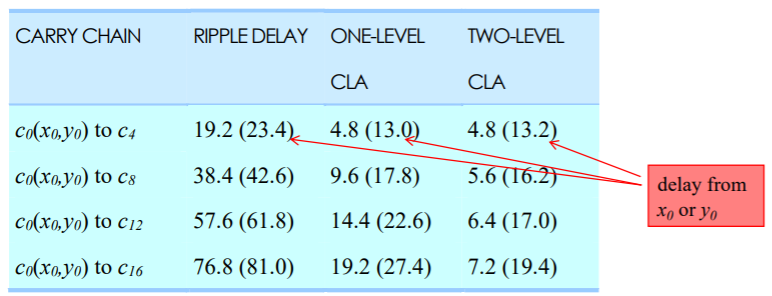

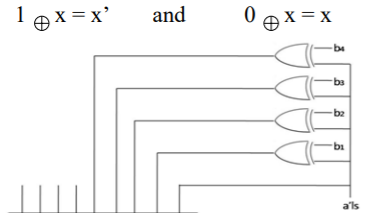

A와 B에 n비트의 input이 들어오고 이때 S값에 따라서 덧셈 혹은 뺄셈을 수행하게 된다.

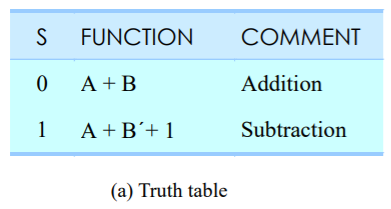

그럼 이것을 회로로 어떻게 구성할 수 있는가 하면

위와 같이 4bit가 각각 모두 입력되어서 출력까지 이어지는 것을 확인할 수 있다. 위의 회로에서는 a'1s 라고 적히어져 있으나 실재로는 위의 논리식에서 나왔던 s를 의미한다.

이때 덧셈 혹은 뺄셈중 어떤 것을 선택하느냐에 따라 위의 boolean function에 맞추어서 값이 입력되는 형태가 되게 된다.

7.3 디코더

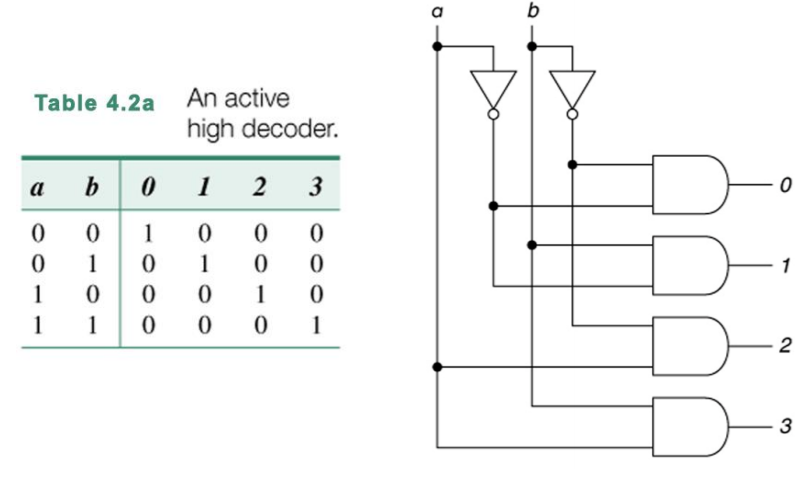

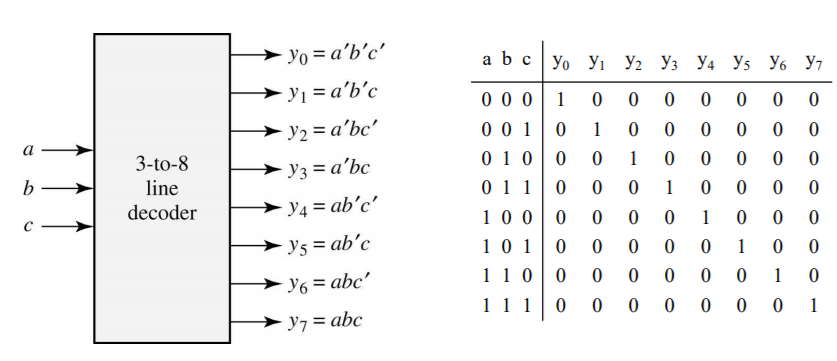

7.3.1 (n x 2^n)디코더

n비트로 된 2진 코드는 서로 다른 2^n개의 정보를 표현하는 조합논리회로이다. 특히 위의 회로는 2x4회로라고 볼 수 있다.(n x 2^n)

이때 위와 같은 진리표를 가지는 회로를 active high decoder이라고 부른다. AND 게이트로 구성된 디코더라고 볼 수 있다.

그렇다면 이러한 디코더는 어디에 사용하는가? 원래 메모리라는 것은 여러개의 bit 들이 들어올때 raw 단위로 들어오게 되는데 이때 특정한 raw를 선택하여서 데이터를 받아들이는 역활을 수행하게 된다.

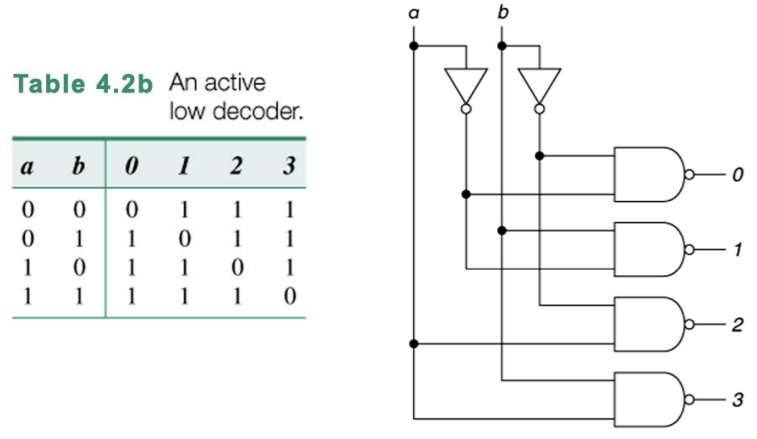

반대로 위와 같은 진리표를 가지는 회로를 active low decoder이라고 부른다. 즉 우리가 선택한 회로가 0으로 나오는 것을 active low decoder이라고 부른다. 이때의 디코더는 nand 게이트를 사용하여 구성된다. 그리고 nand 게이트의 특성상 active high decoder에 비해서 빠르다.

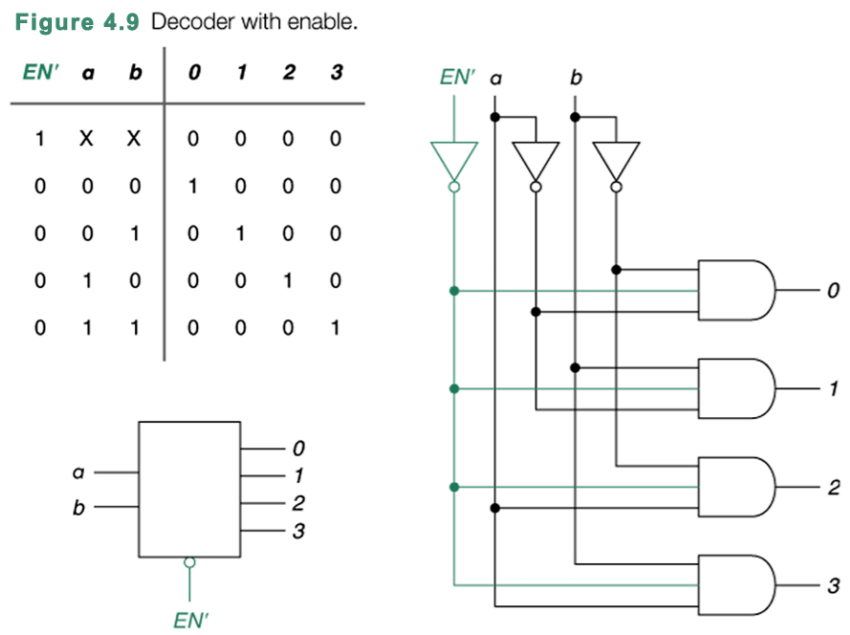

또한 입력 값으로 하나의 Signal을 추가로 받을 수 있는데 이를 EN'이다. EN'이 1이면 Select가 되지 않았다는 의미이고 EN'이 0이면 Select하고 있다는 의미를 가지게 되어 출력값이 결정되게 된다.

그래서 최종적으로 나온 것은 3-input and gate이다.

이것을 확장하여서 3x8 decoder을 제작할 수도 있다.

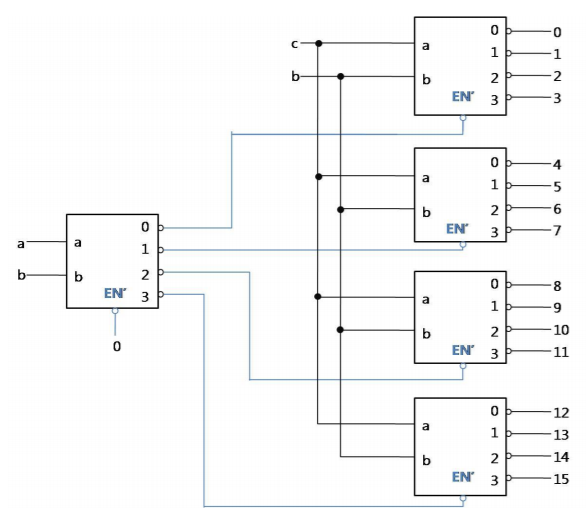

혹은 이걸 또 확장하여서 4x16 decoder을 제작할 수도 있다. 이것은 이렇게 해석할 수 있다. 0이 선택되었다면 1이 반환되어 가장 위쪽 decoder로 올라가게 되고 거기에서 다시 1로 바뀌어 출력을 결정하게 된다.

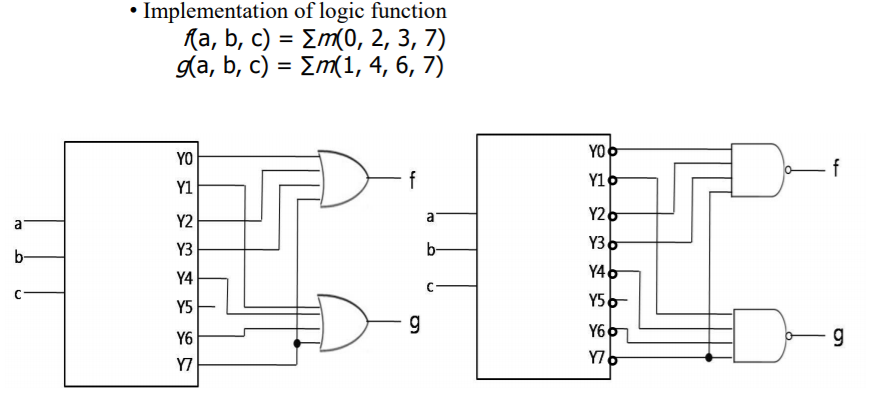

7.3.5 디코더를 이용한 조합논리회로

위의 예시는 3x8 디코더가 3개의 입력을 8개의 출력으로 바꾸기 때문에 이들 최소항을 조합하여 출력을 결정하면 원하는 회로를 쉽게 구성할 수 있다.

또한 위의 그림에서는 or을 nand로 바꾸는 과정역시 함께 보여주고 있다.

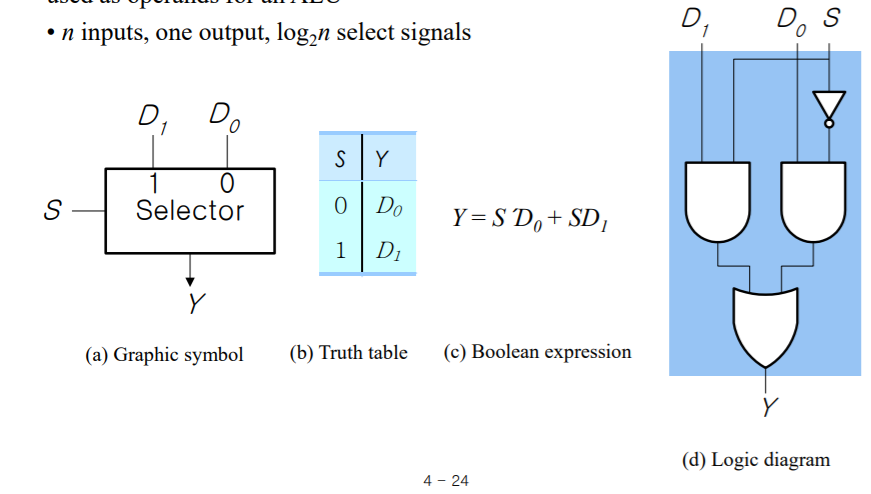

7.5 멀티플렉서

멀티플렉싱이란 다수의 정보 장치의 데이터를 소수의 채널이나 선을 통하여 선택적으로 전송하는 것을 의미한다. 여기에서 n 입력은 하나의 출력이자 logn의 선택 신호를 가지게 된다.

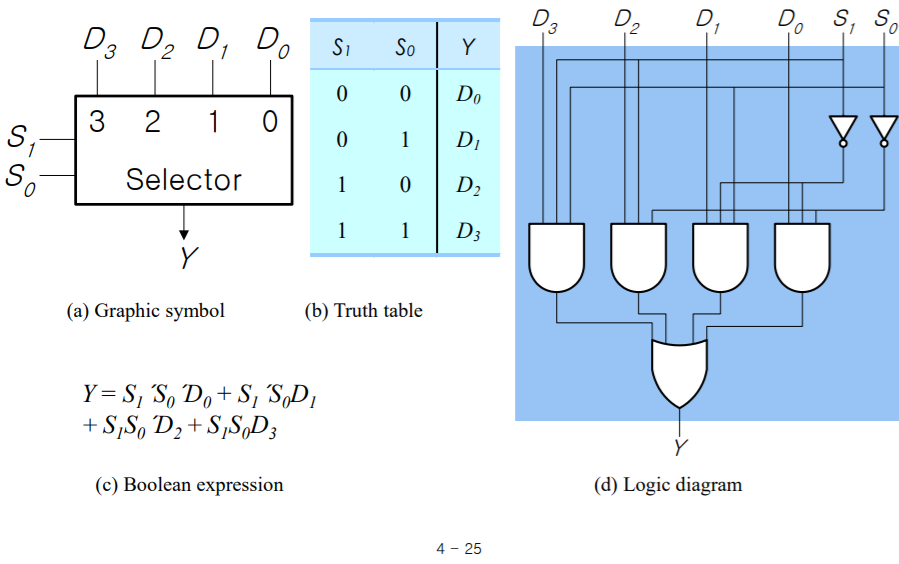

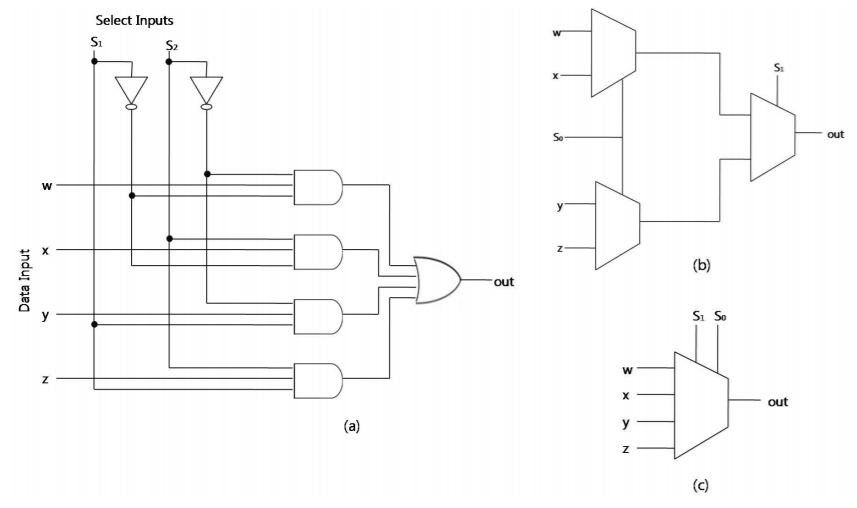

7.5.2 4x1 멀티플렉서

4개의 입력은 2개의 입력 선택기로 출력을 내보내게 된다.

이때 멀티플렉서를 구성하는 방법은 두가지가 존재하는데 통으로 4x1 멀티플렉서를 제작하거나 혹은 2x1 멀티플렉서 2개를 사용하는 방법이다.

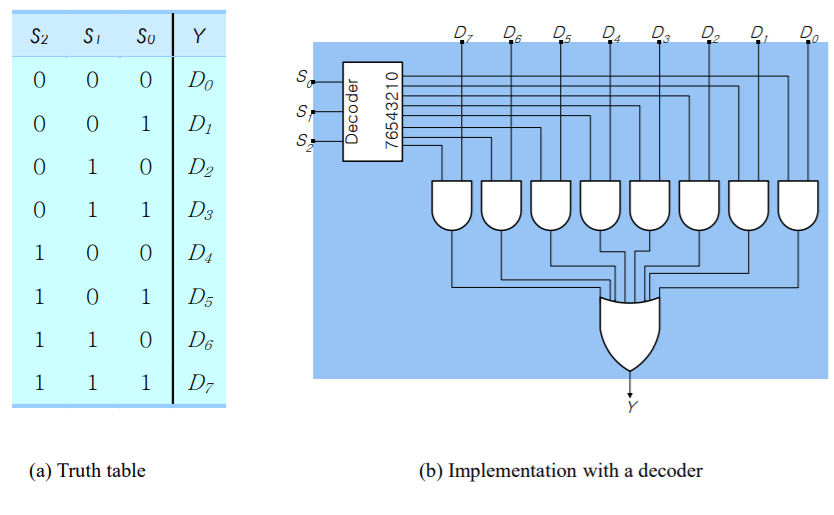

7.5.3 8x1 멀티플렉서

또한 8개의 인풋을 가지고 하나의 출력을 내놓는 멀티플렉서를 만들 수도 있다.