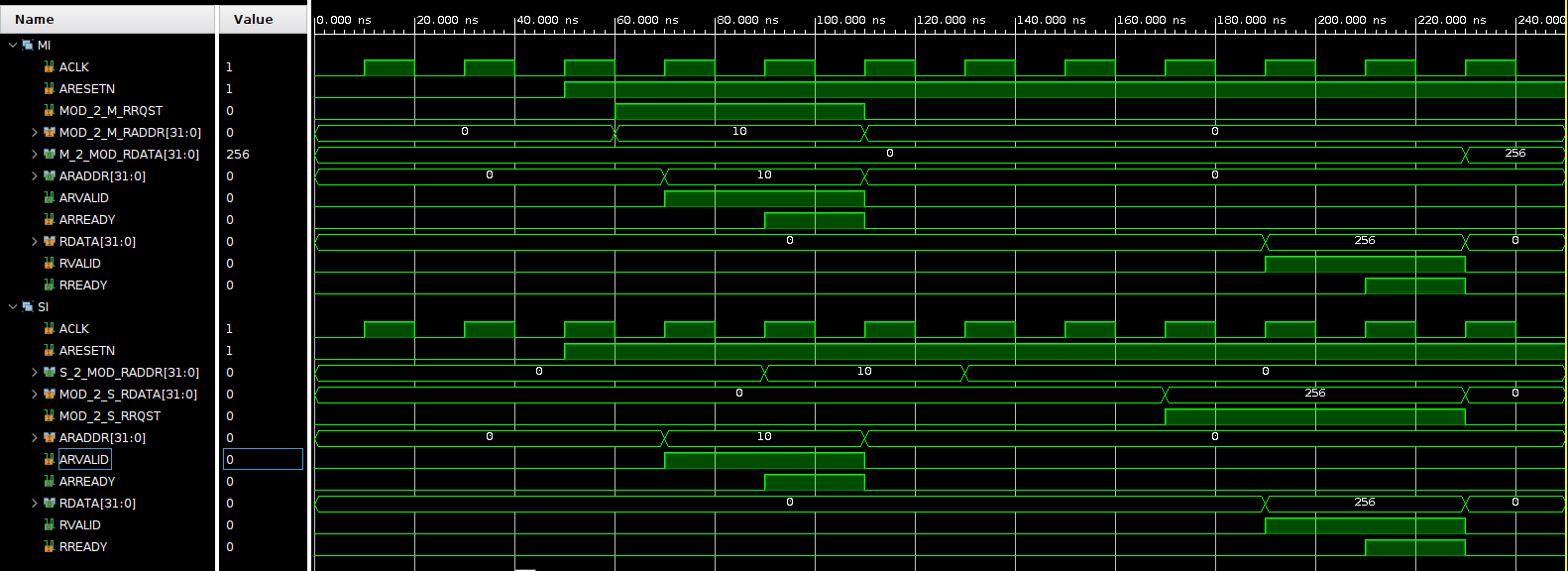

AXI_Lite_Read_Channel Source & Testbench Code

우선 현재는 Read Channel만 구현된 미완성 인터페이스이다. 그리고 Vivado에서는 SystemVerilog의 Interface 명령어를 지원하지 않기 때문에 코드가 좀 길어진 면이 있다. 만약 Write Channel까지 구현한다면 더 길어질 것이다.

또한 실제로 모듈에 Interface를 적용할 때에는 외부 Stimuli를 통해서가 아닌 모듈을 내부에서 Stimuli를 주는 방식으로 Testbench를 구성해야할 것이다. 하지만 이렇게 코드를 작성하면 Stimuli를 readmemb 등의 명령어를 통해 Stimuli를 주어야할 것이다.

개선하고 싶은 사항:

1. CDC 가능하게 설계.

2. Master쪽에서 Request를 보냈는데 못받았을 경우 Error output 띄우기.

의문점:

보통 Handshaking방식이라하면 우선 서로 연결되었음을 확인하고 Data를 Transfer하는것으로 알고 있음. 그런데 이번에 설계한 AXI Lite에서는 Valid와 동시에 Data를 전송함. 사실 어차피 Timing Violation만 일어나지 않으면 상관 없을 것 같긴함. TCP/IP와 HW에서의 Handshaking의 차이인 것으로 보임. 그런데 아주 만약 Valid와 Data의 시간차이 때문에 동시에 도착하지 못했다면 저렇게 Valid신호가 도착했다는 것 만으로 연결을 끊어버려도 되는 걸까? 또한 반대편도 마찬가지로 Ready를 풀어버려도 되는걸까? 이에대한 조사를 좀 더 진행해봐야 알 것 같지만 아마 모든 Timing Constraint를 만족한다는 가정하에 설계하기 때문에 차라리 Clock Speed를 낮춰서 Timing을 맞추는 방식으로 설계할 것으로 생각된다.