질문)

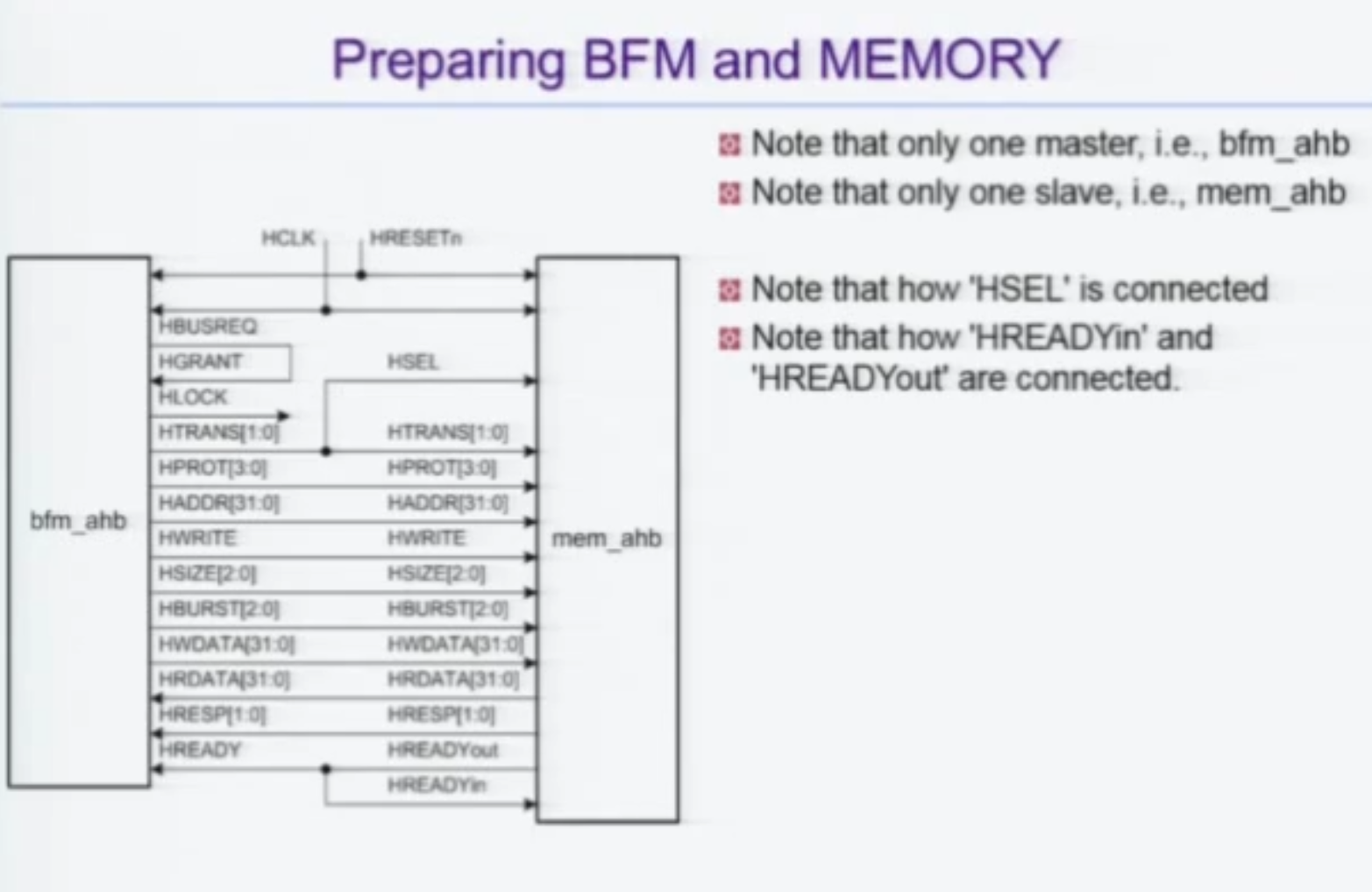

슬레이브마다 HREADYin out 모두 있는데, 대표성이 있는 값을 중재하는 부분이 누구인가? 마스터인가 아비터인가 디코더인가?

답) 마스터는 HREADY 를 반드시 봐야하고, 슬레이브는 당연히 HREADY를 출력할 것. 이 때, 슬레이브는 모든 HREADY 신호를 OR 로써 피드백해 다시 받아들인다.(?!?!? 그러면 전부 0이지 않는 한 1로써 in 되게 되는데?)

따라서 짤 때, HREADY를 항상 1로 유지해야한다.(기본출력을 1로 하되, 엄밀하게는 OR 로 놓으라는 것으로 이해했다)

Introduction for AMBA 5 AHB5

그런게 있다고 한다.

Security 관련된 properties 가 여럿 추가되었다고 한다.

근데 HW Security 라는건 솔직히 잘 이해가 되지 않는다. 오프라인에서 접근하지 않는 한 어떻게 HW 를 해킹한다는 말이지?

Exclusive Access Monitor

Slave 가 "마스터님이 보내준 명령어 처리하는데 아무도 안건들였어요" 를 표시하기 위한 EXCLUSIVE OKAY 신호.

만약 누가 건들였다면 OFF된다.

애초에 Exclusive 한 작업의 경우 누가 찝쩍거려도 100% 씹는게 보장되게 짜야지, ON/OFF 해서 마스터에게 보고하는게 의미가 있나?

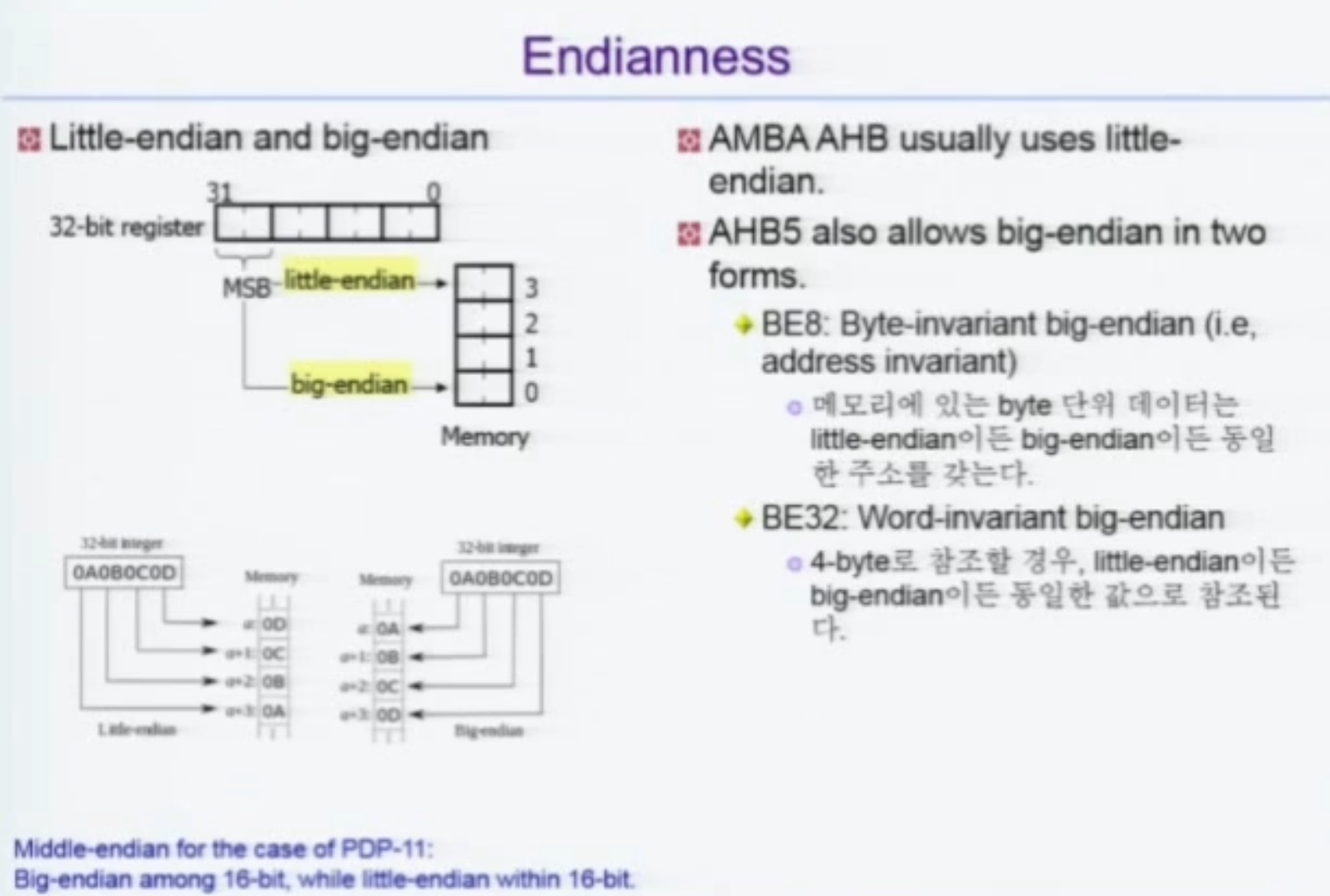

Big Endian 의 종류

Byte Invariant Big Endian(BE8)

Word Invariant Big Endian(BE32)

Data Invariant 를 통해 Little Endian 이던지 Big Endian 이던지 무결성을 보장할 수 있다.

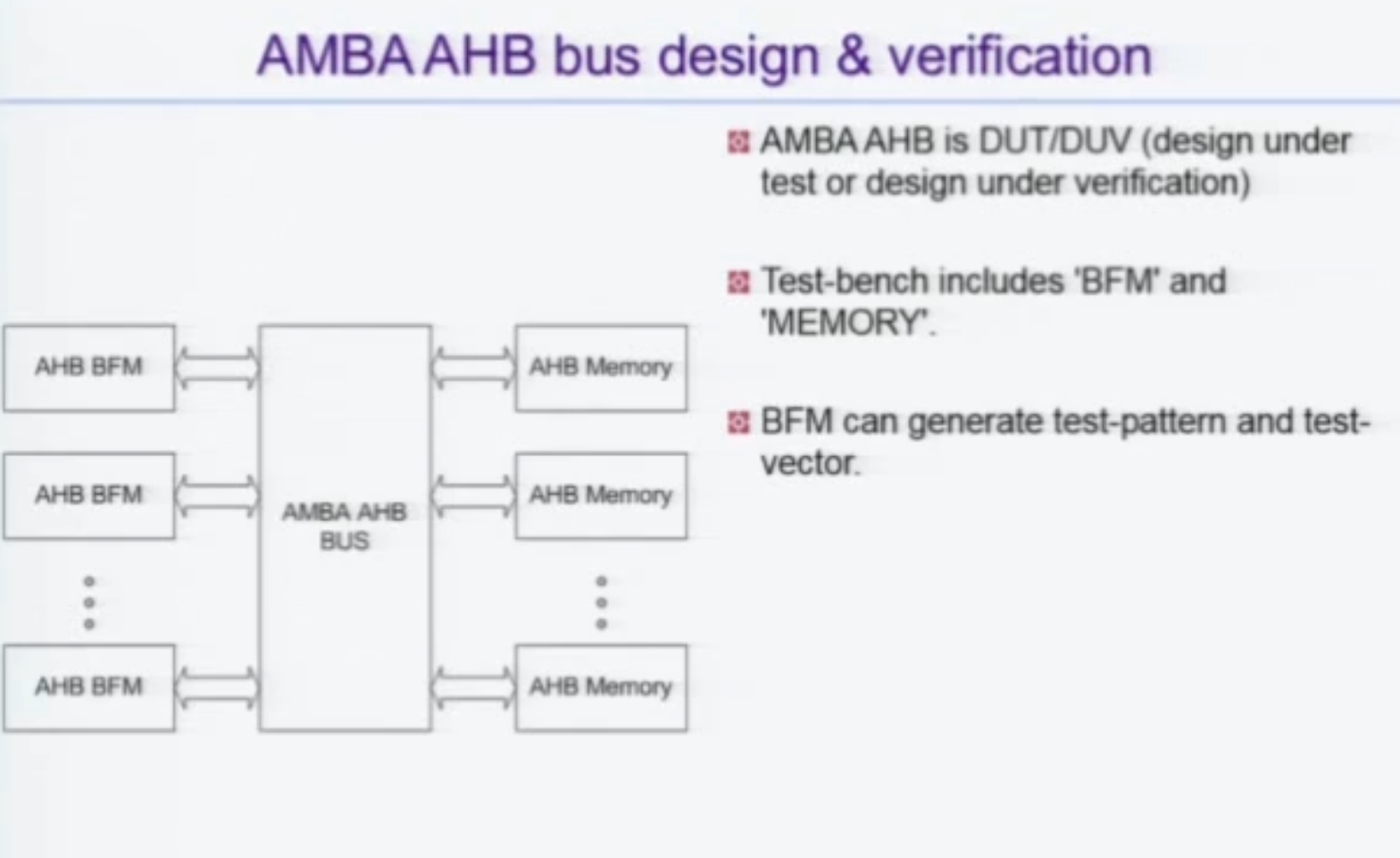

AMBA AHB BFM Design

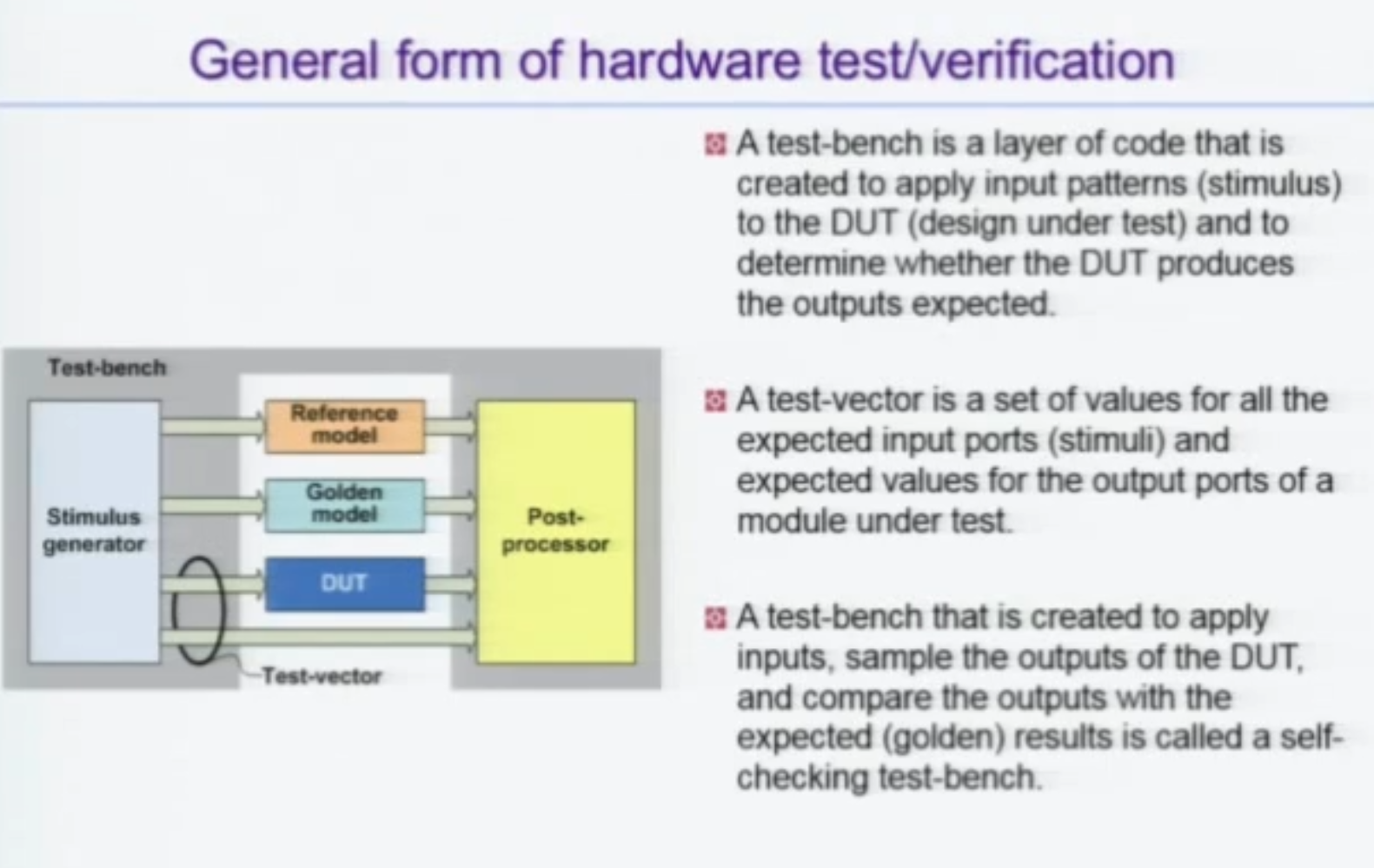

기존의 배운 Test 구조

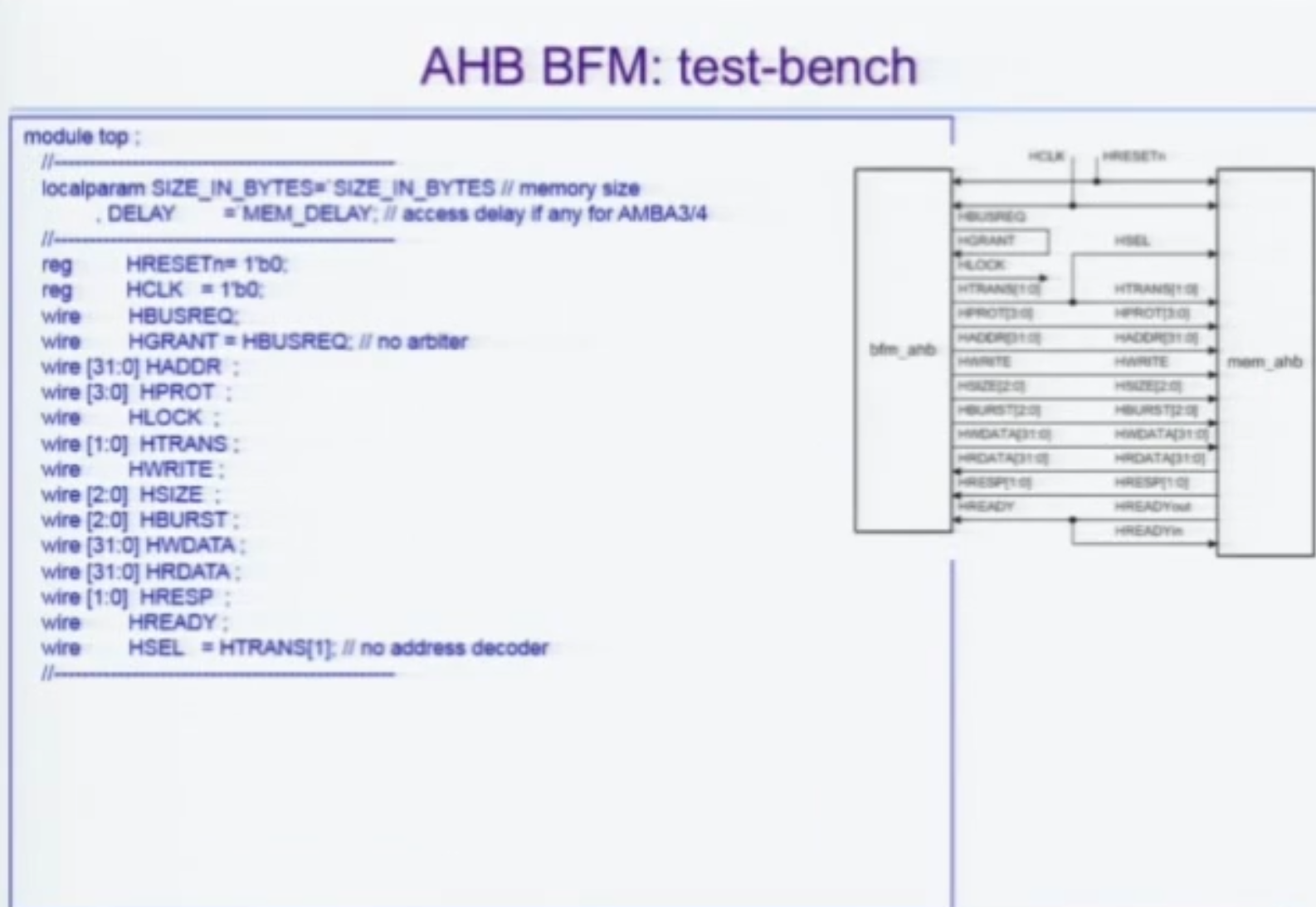

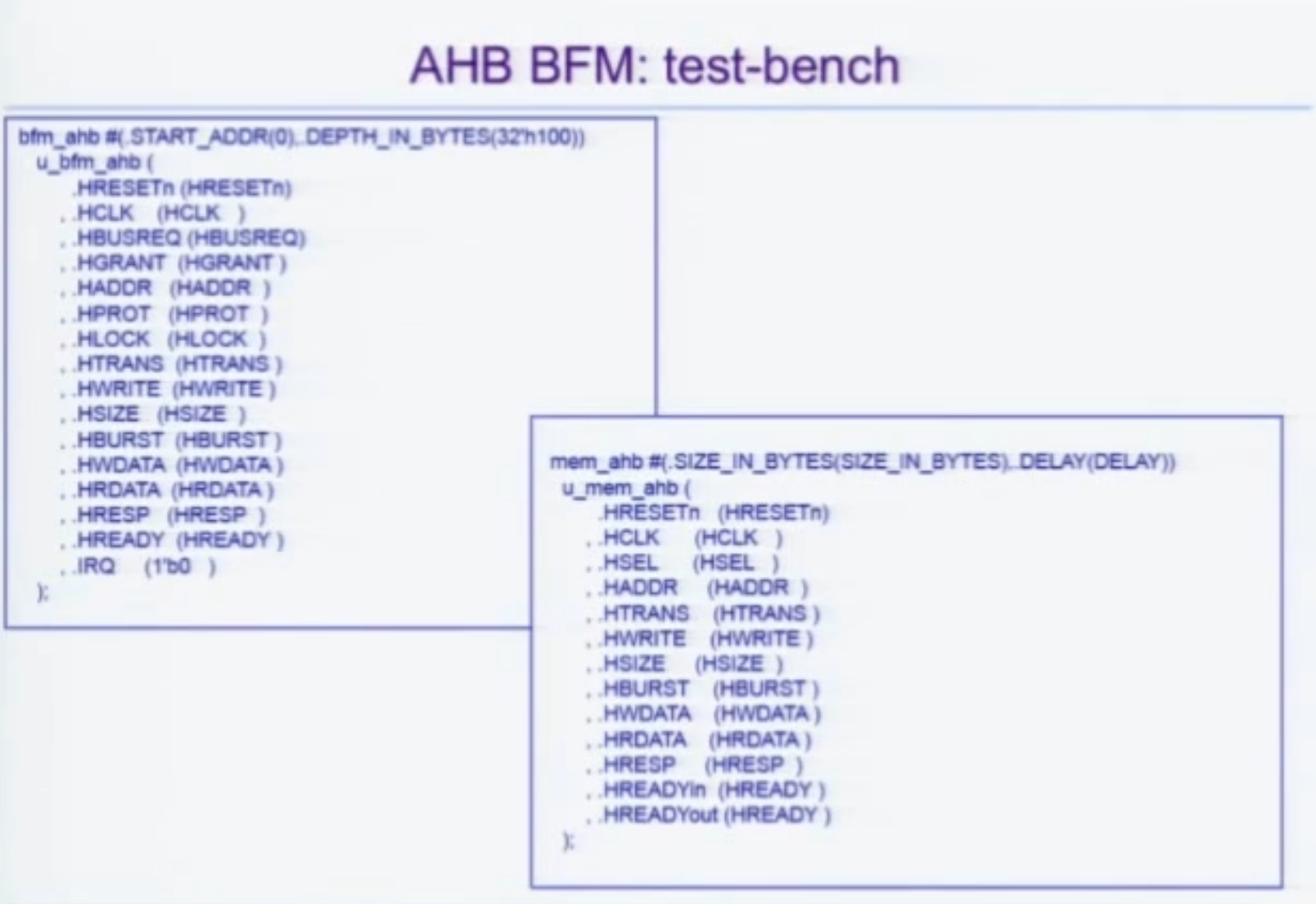

BUS 평가를 위한 AHB_BFM과 AHB_Memory 모듈

대조군 설정 - Bus없는 testbench

1:1로 연결이 안되는 Port 의 경우 위처럼 HTRANS의 IDLE 여부만 HSEL 로 빼고, 이런 식으로 알아서 조율한다.

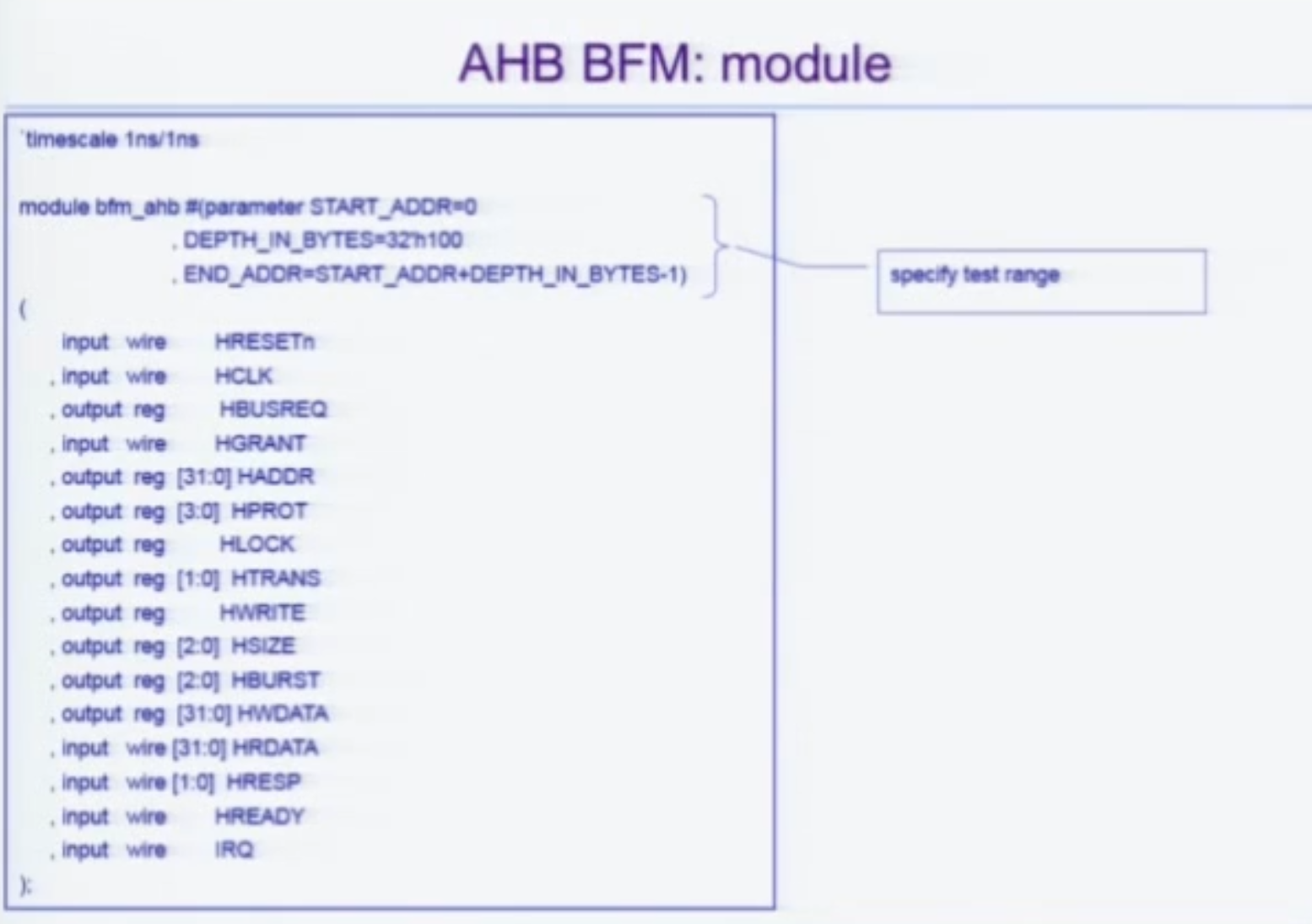

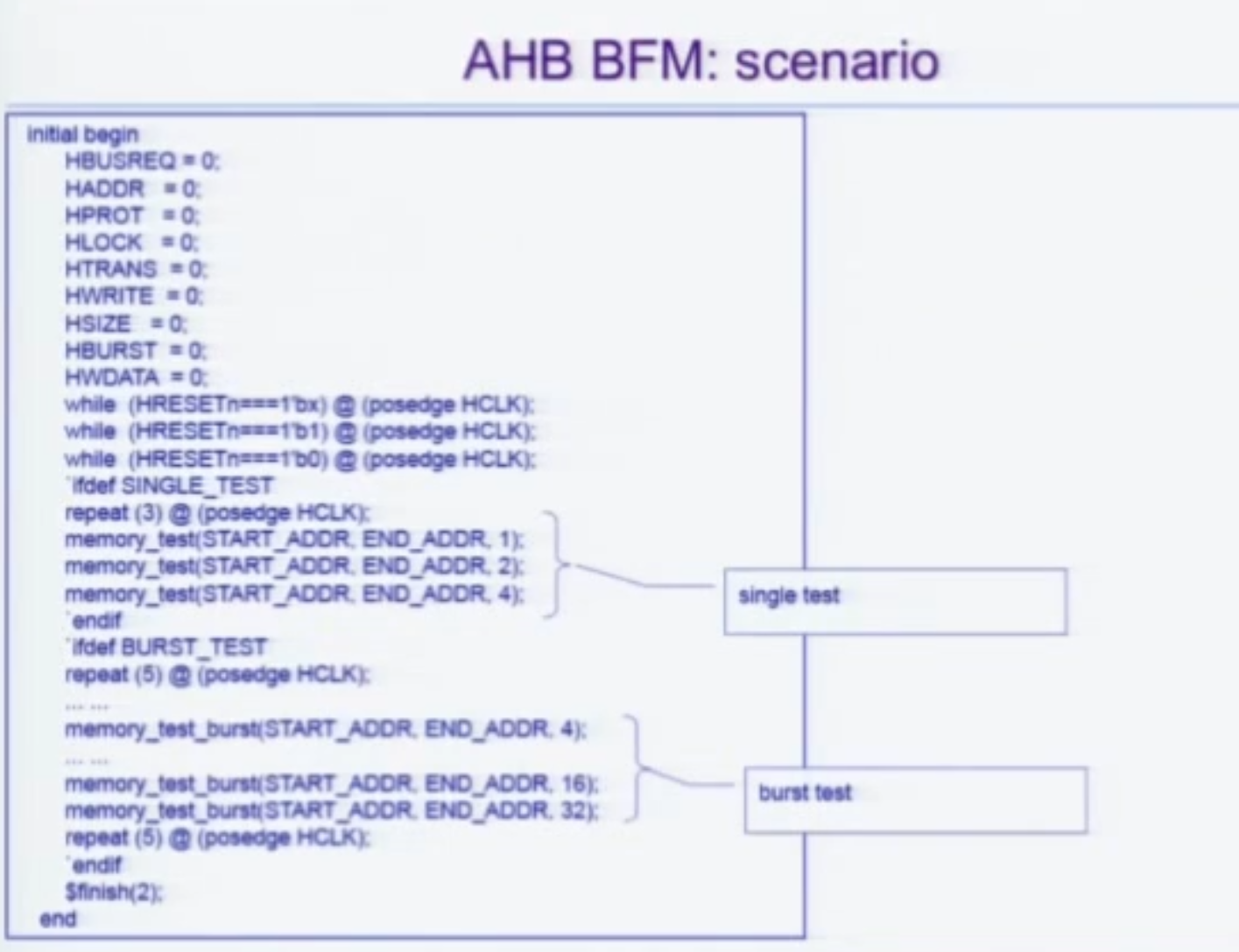

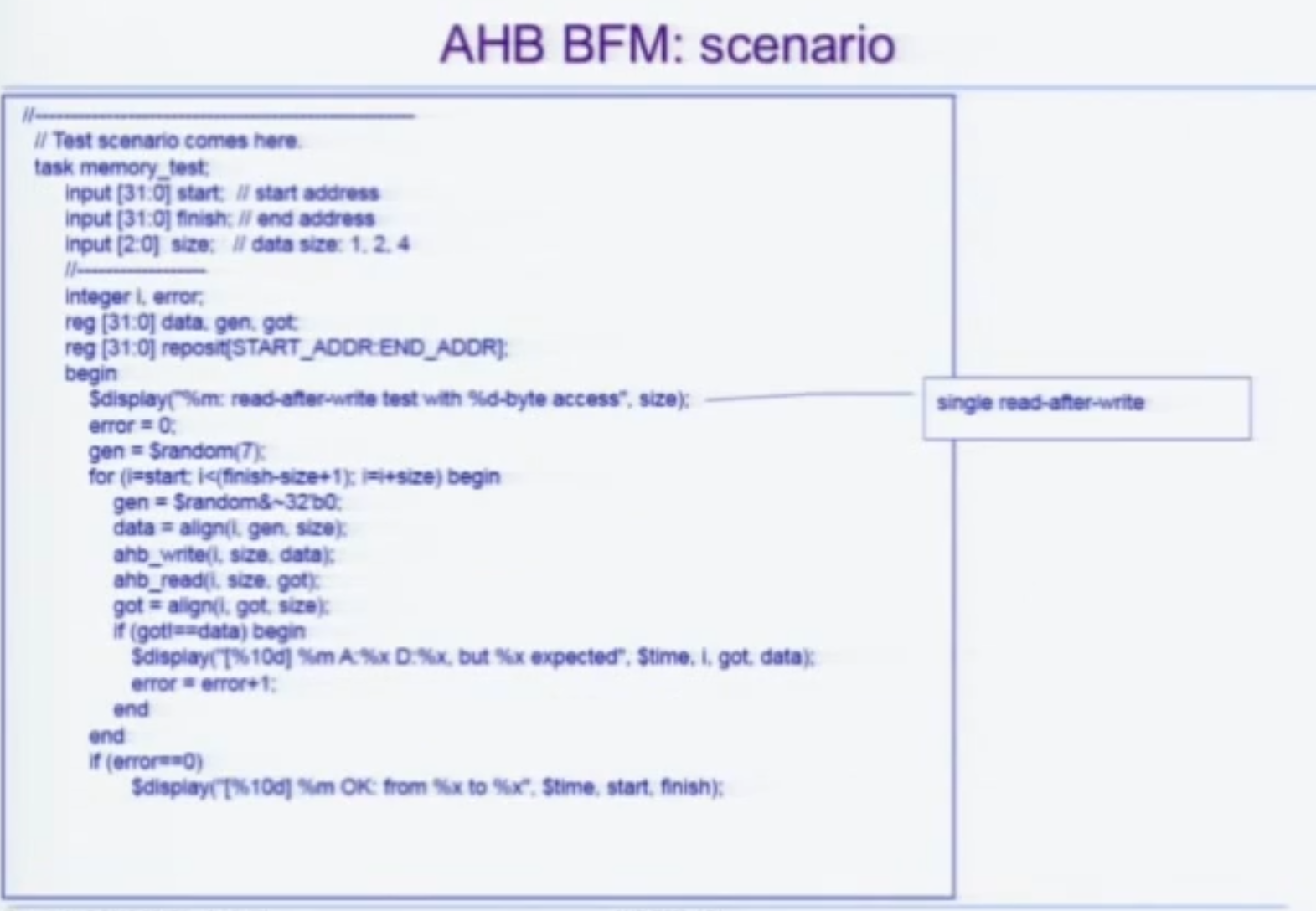

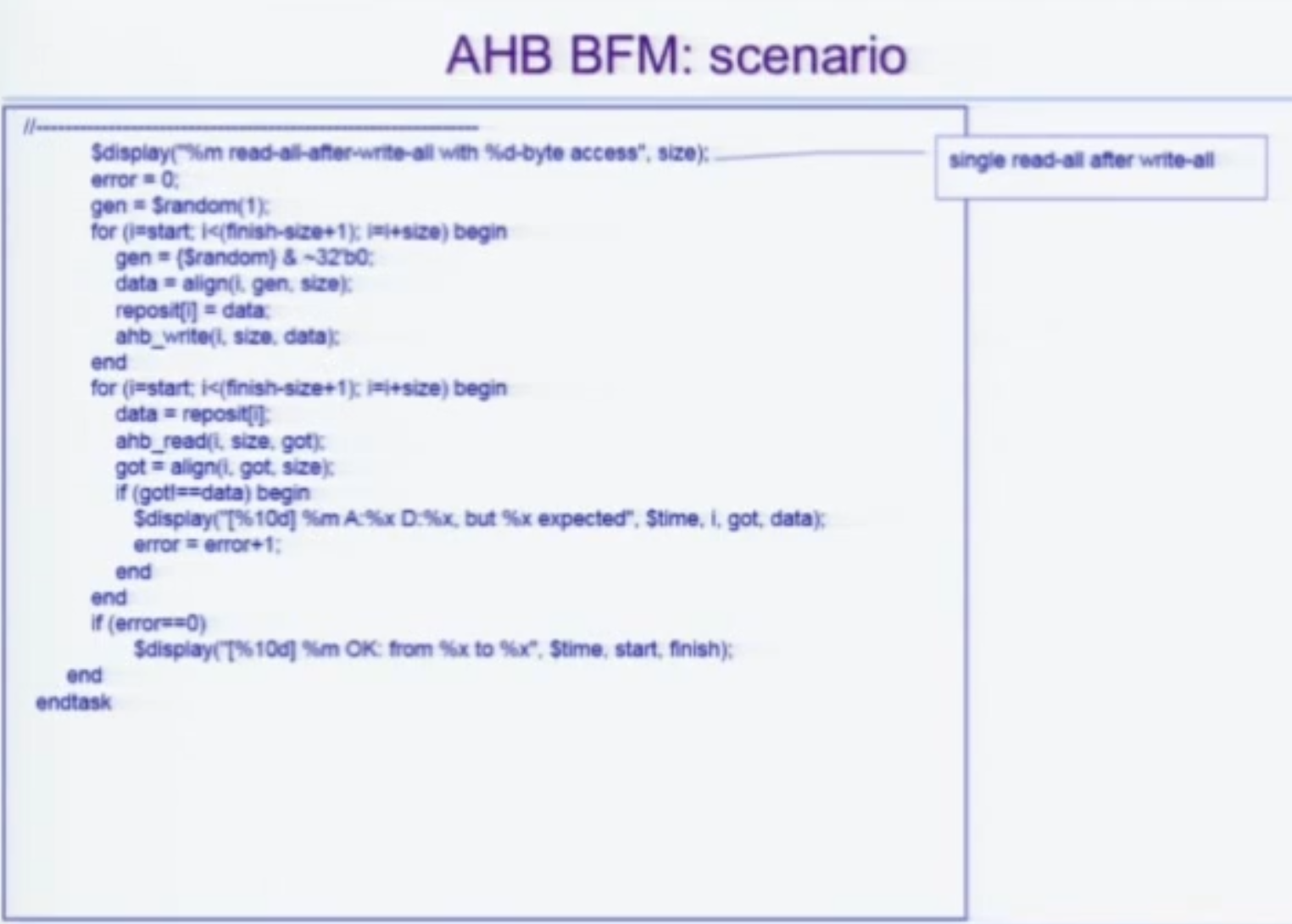

구현 코드 예시

나중에 참고하자.

testbench 인수 선언

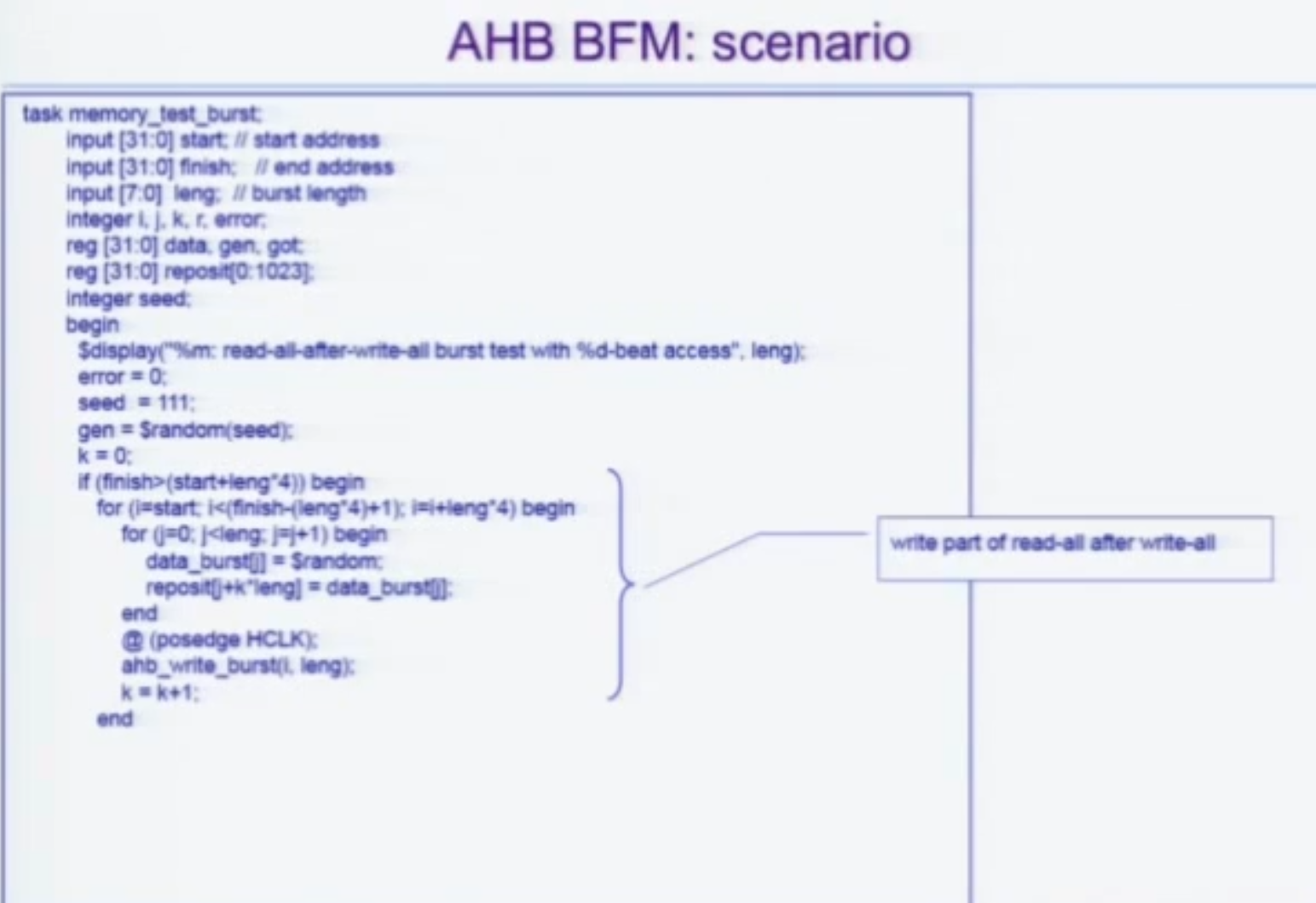

testbench 시나리오 정의

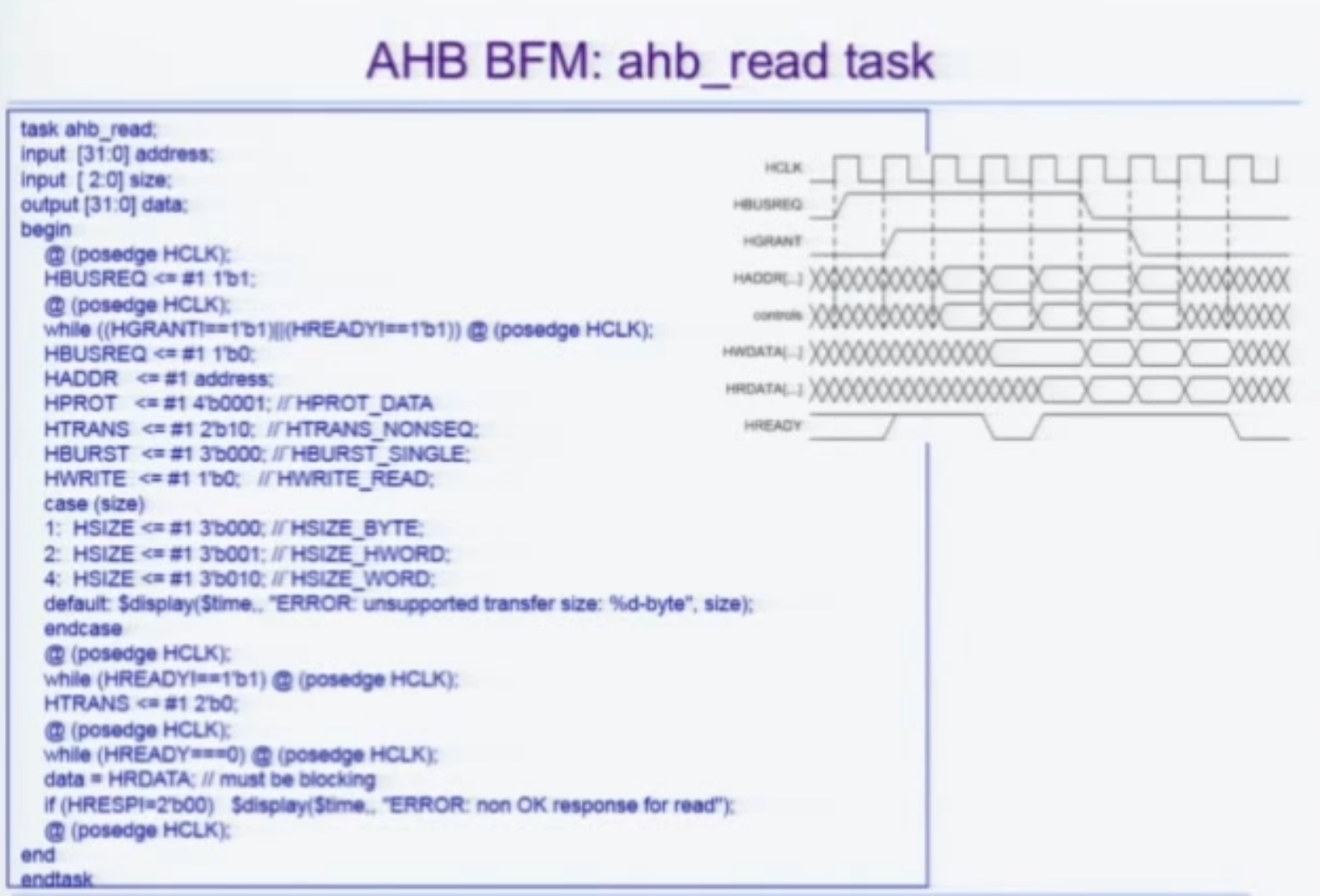

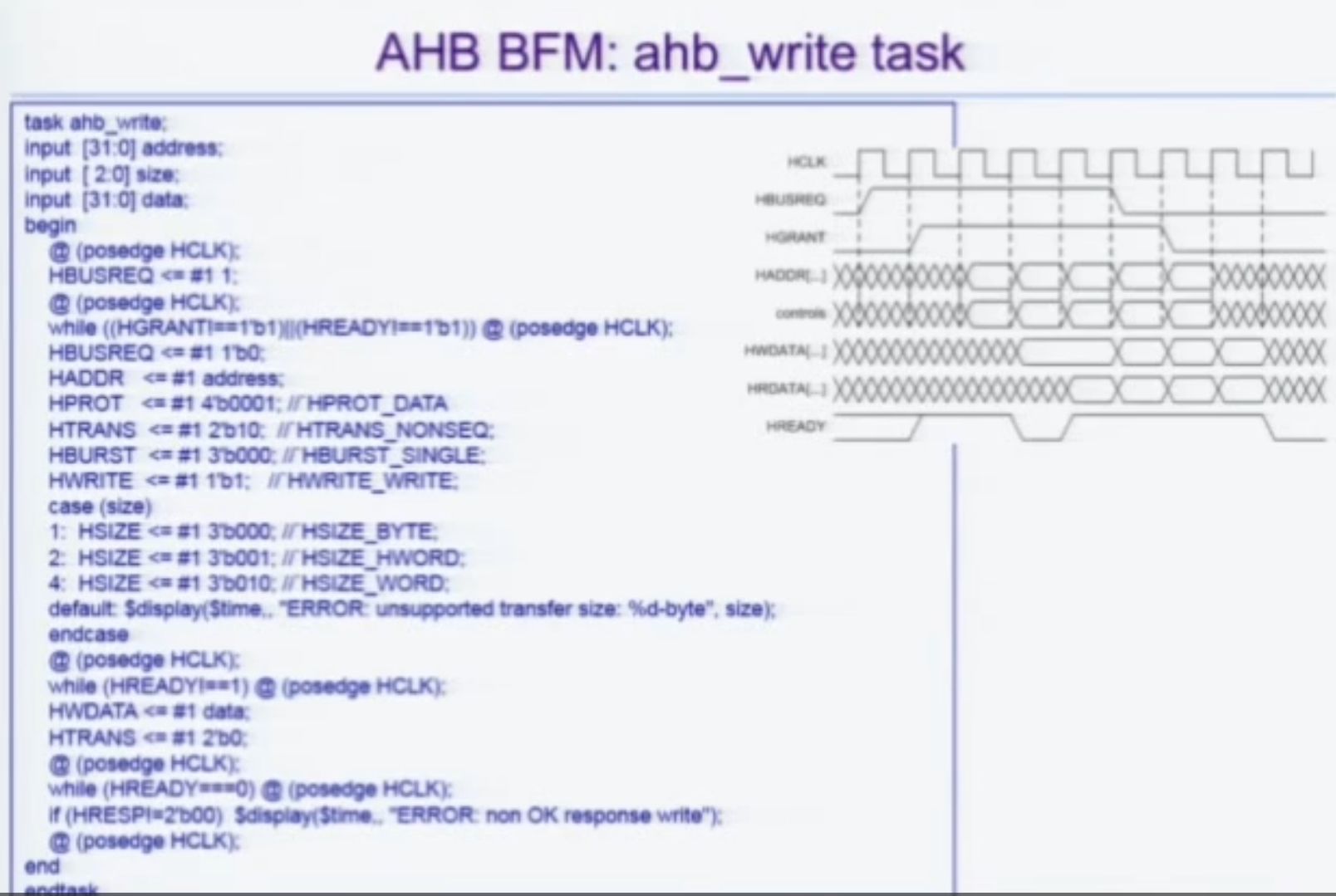

task 정의

display 를 통해 제대로 시나리오가 진행되었는지를 용이하게 체크할 수 있다.

BFM

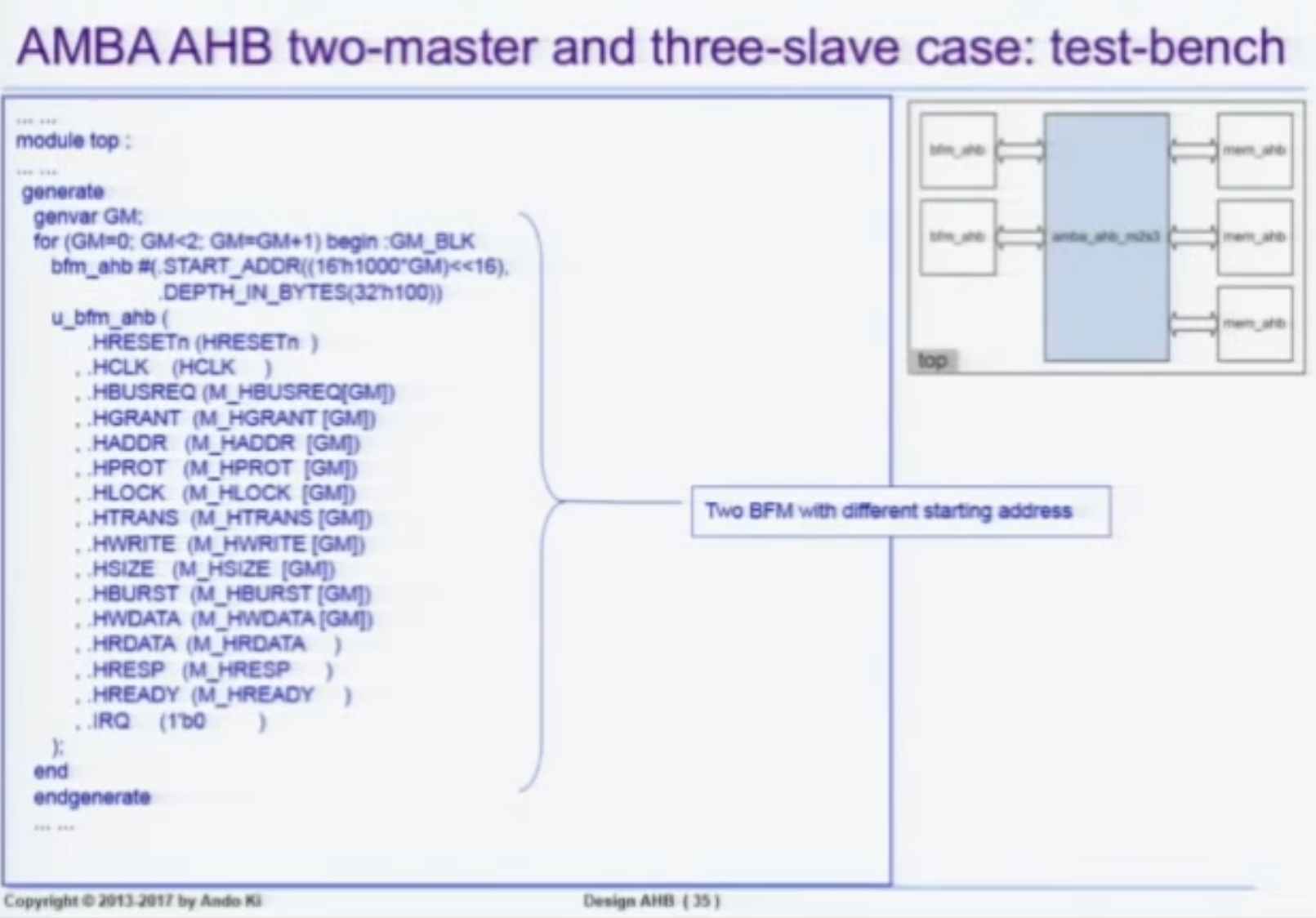

최종 테스트벤치이므로 아래처럼 두 모듈이 선언됨을 볼 수 있다.

클럭선언 및 VCD를 확인할 수 있다.

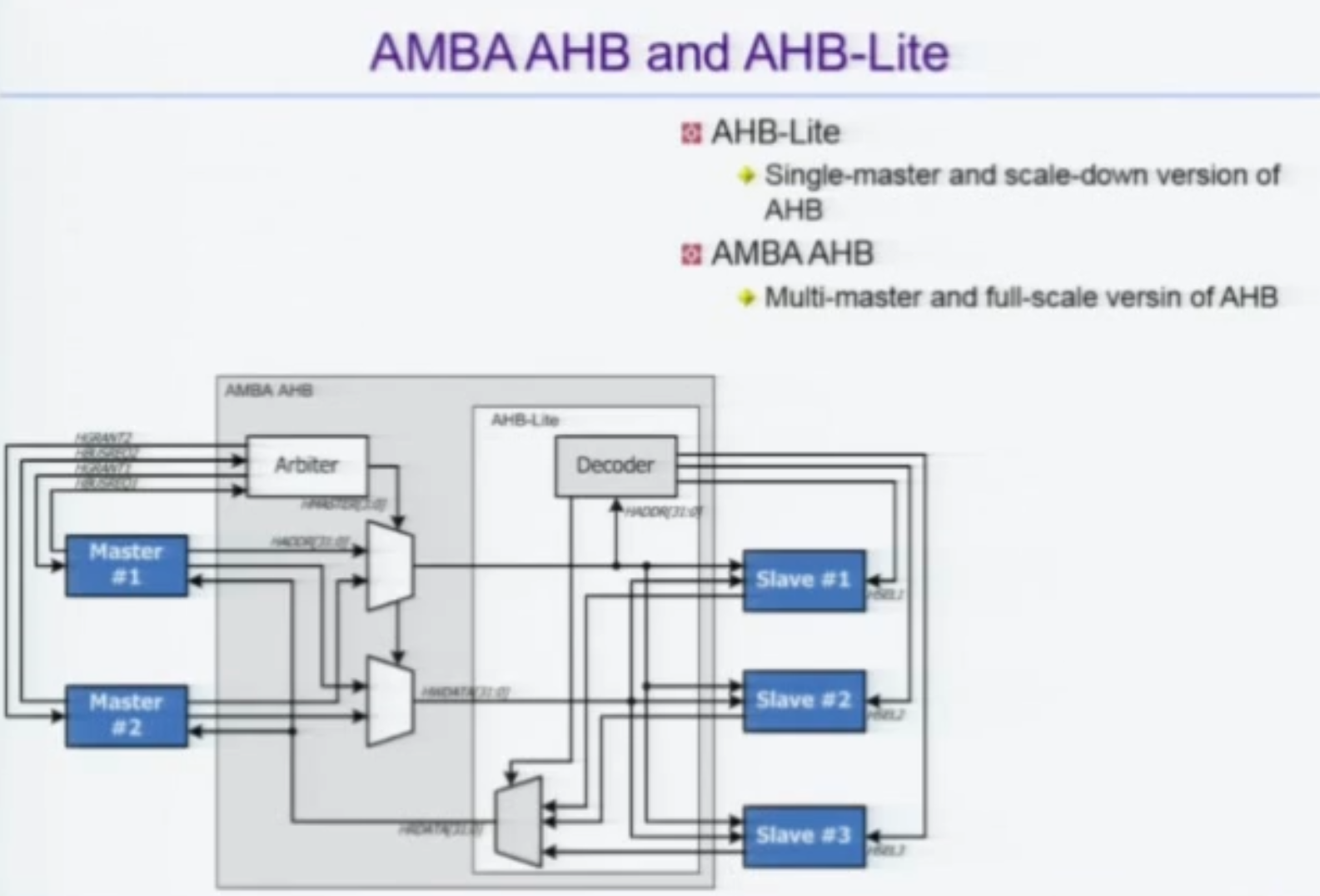

2-3 AMBA AHB Design

개요도

구현예시

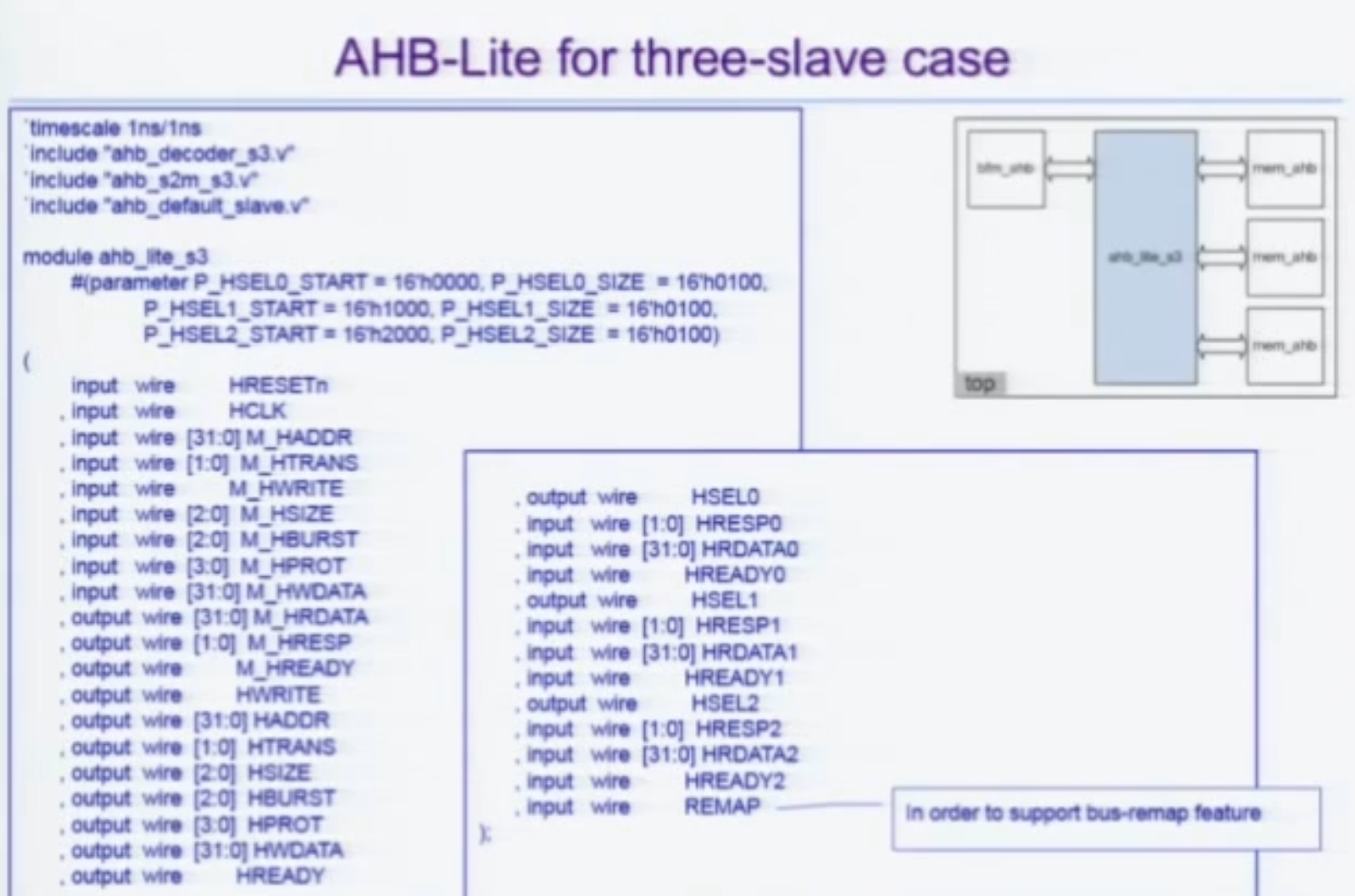

AHB-Lite

여러 Master 와 Slave 의 generate 를 통한 간편한 인스턴스화

Addressing Remapping

SRAM, FLASH 등등 여러 장치가 주소를 공유하는데, 주소공간을 SWAP하는 것.

예를 들어, ARM은 부팅할때 Flash의 0번지는 부트스트랩 관련코드가 있어야하는데 속도를 위해 먼저 SRAM으로 옮긴 뒤 SRAM 첫주소를 0번으로 SWAP하기도 한다.

2-4 Design and Verification of AHB2APB

해당 강의에서는 Bridge 설계에 대해 다룬다.

아직 이 진도까지는 URP 프로젝트가 나가지 않은만큼

이 강의부터는 다음 포스트부터 다루기로 한다.

드는 의문사항

앞으로 강의 중 드는 질문사항은

로 표기하기로 했다.