6.5학기

1.[Verilog] generate & genvar를 통한 코드 간소화

Verilog 에서 For 문은 전처리기에 의해 처리되는 일종의 매크로문이다.레지스터 X0~X31 전체에 대하여 수행되는 연산이 있다고 할 때, 모든 레지스터에 대하여 일일히 작업을 적어넣는다면 이는 번거로울 것이다.위 코드는 reset이 발생했을 시 모두 0으로 초기

2.[Verilog] +: 의 의미

위 문법의 의미는 Vector bit-select and part-select addressing 이라는 것이다.만약 아래 코드에서마지막줄의 동작은sel이 0이면 sel이 7이면 가 된다.좌측의 숫자는 starting index 를 가리키고, 우측의 숫자는 width를

3.[Verilog] register 의 2nd array 선언

Verilog 는 꼴로 선언이 가능해 어디가 1차원, 2차원, 3차원인지 간혹 곤혹스러울 때가 있다.이 때, 첫 7:0 의 의미는 자료형의 크기로 보면 되며둘째 및 셋째 인덱스의 의미는 기존 C의 것과 동일하게 해석하면 된다.만일, reg 7:0 a0:3 가 있다면 이

4.할것 임시 메모

Icarus Verilog 로도 Simulation 해보고 파형분석 해봐야 함

5.[WSL2] Windows Terminal 에서의 zsh 환경 세팅

WSL2를 위한 zsh 환경세팅을 기록하고자 한다. WSL2 방지해제해야함 Ubuntu 윈도우스토어에서 다운로드, Windows Terminal 다운로드 zsh 설치 zsh autocomplete 설치 zsh highlight-syntax 설치 zsh 타임스탬프 설치

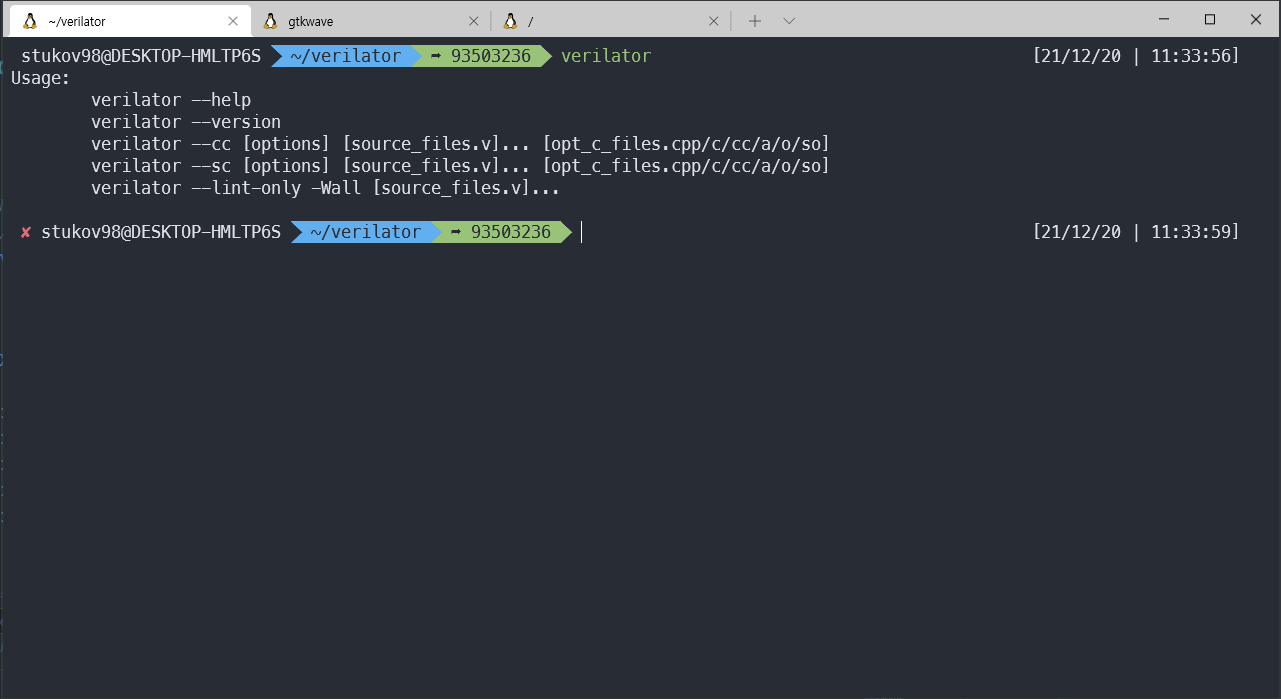

6.[Verilator] Verilator 설치 및 환경설정

※본 포스트는 학부생이 공부용으로 작성한 포스트이며, 확실한 사실을 보장하지는 않습니다.여러 일이 있었는데,컴퓨터에 대해 내가 이해한 모든 것을 Verilog 로 구현해보고자 하였다. 구현하지 못한다면 제대로 아는 것이 아니라고 생각하기 때문이다. 또한 잘 구현된다면

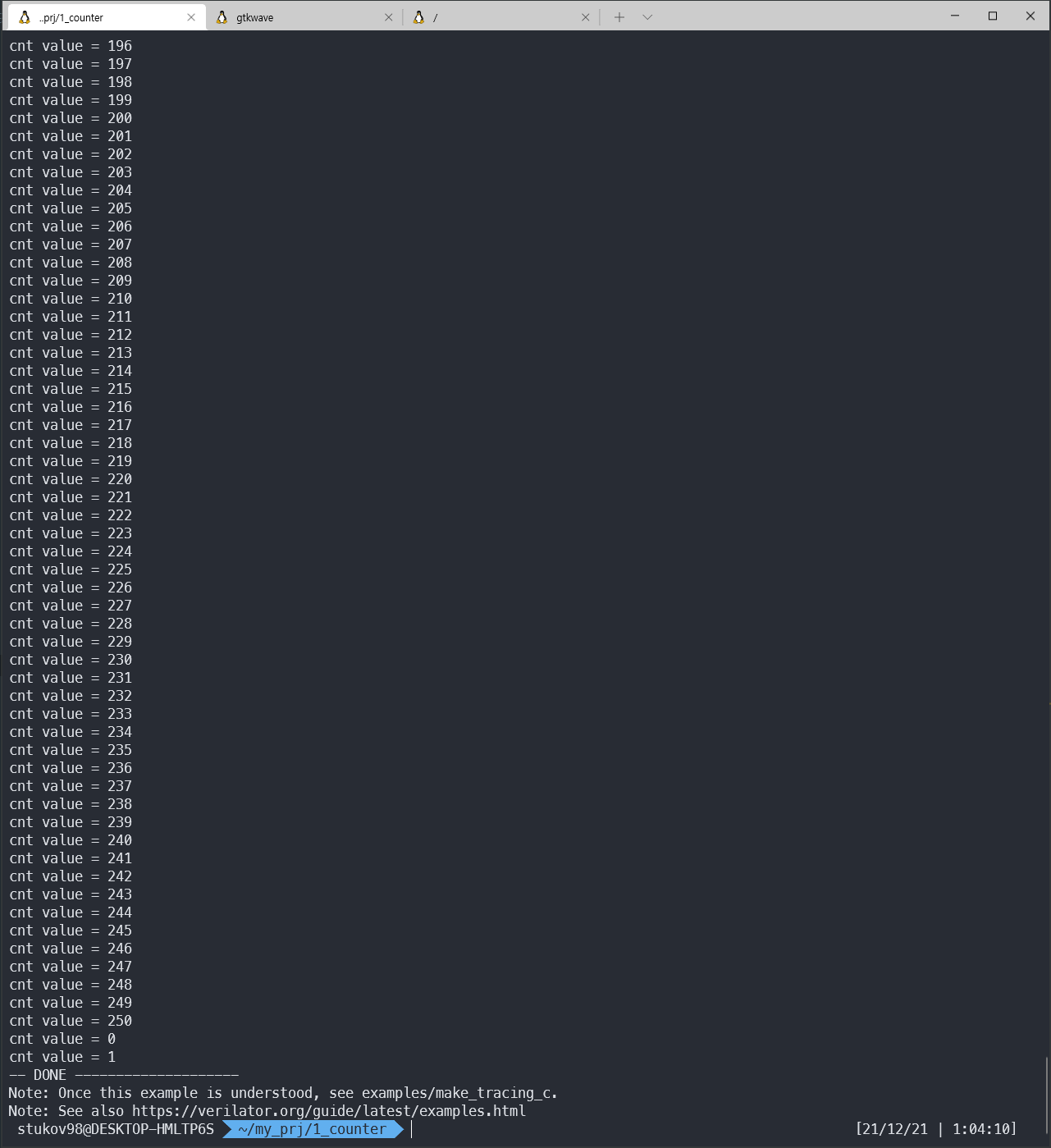

7.[Verilator] make_hello_c 코드 분석 및 counter 구현

앞서 코드의 의미를 분석해보고자 한다. 참고했던 네이버 블로그와 내용이 다를텐데, 이는 verilator 버전이 1년이 넘어 대대적으로 바뀌었기 때문으로 추정한다. 우선 makehelloc를 ~/my_prj 로 복사한다. -f없으면 mkdir 따로 해야해서 귀찮을

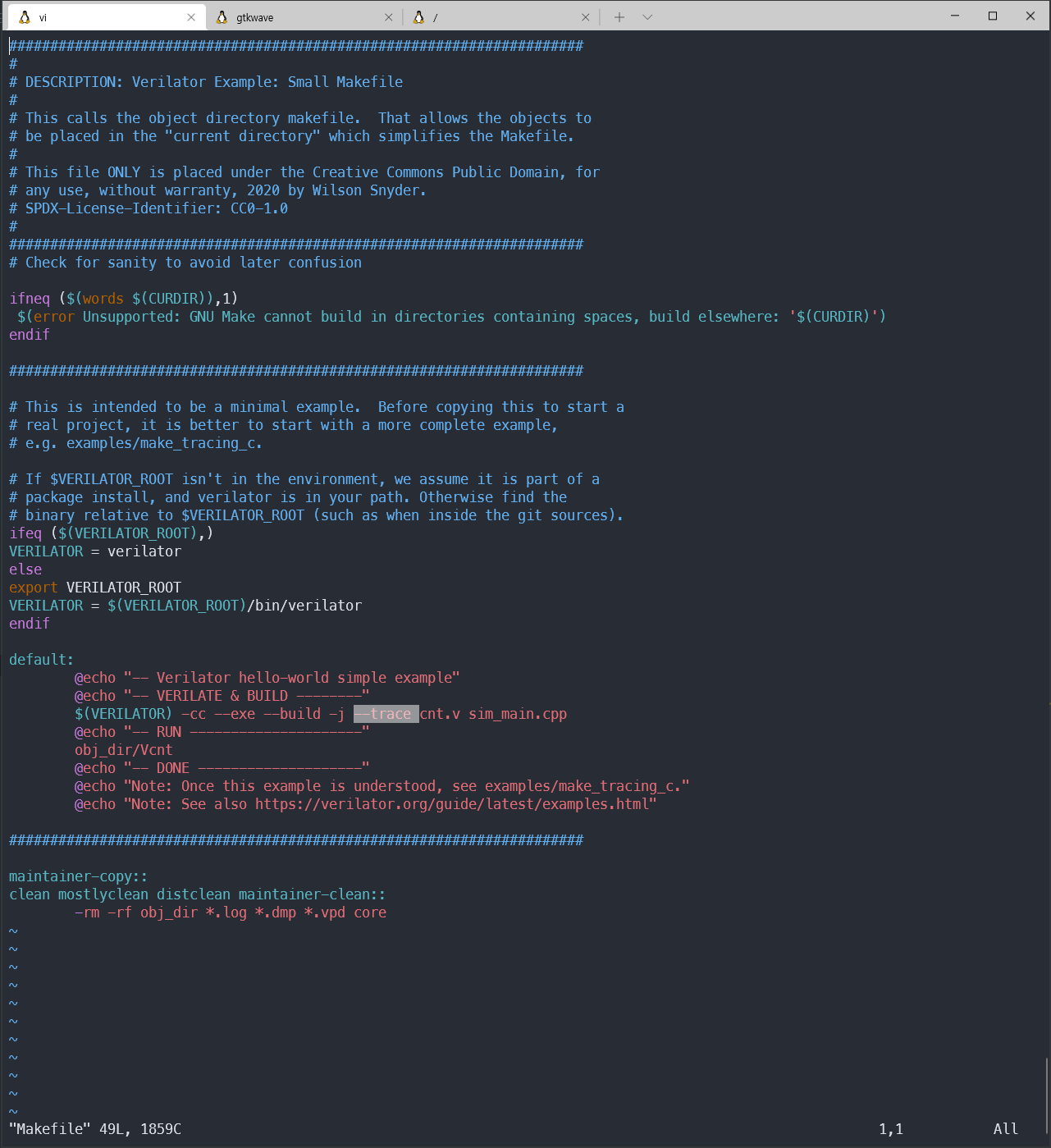

8.[Verilator] --trace 를 통한 .vcd 생성 및 gtkwave 를 통한 파형 확인

앞서 top->eval() 의 의미 및 verilator 내부 변수구현구조에 대해 간단하게나마 알아보았다.이제는 gtkwave 를 통해 파형을 확인할 것이다.참고로, WLS2 에서 윈도우로 GUI 를 띄워야 하기 때문에,X11 윈도우 설치 및 세팅이 완료되어있어야 한다

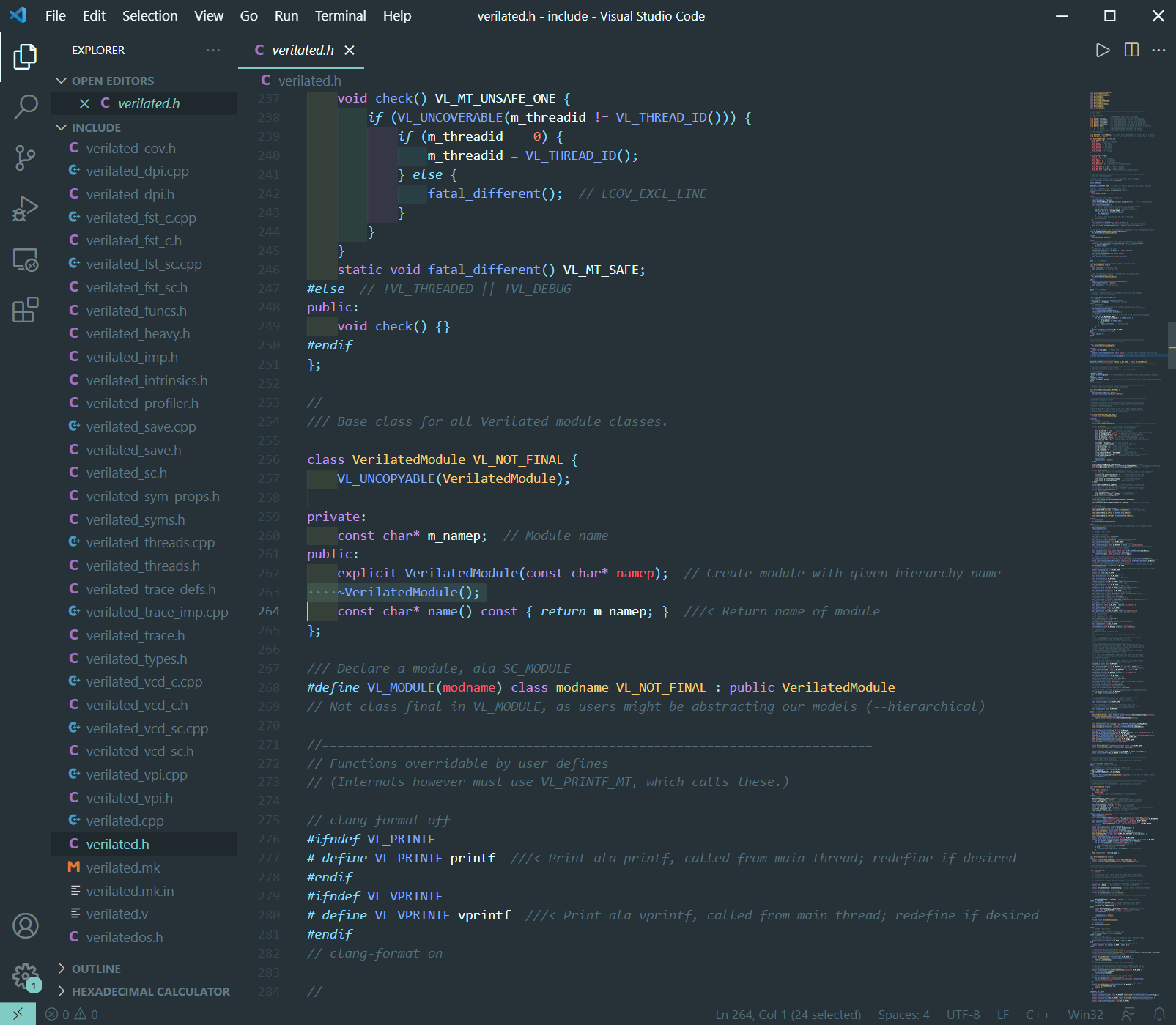

9.[C++] virtual destructor 사용의 이유

Verilator 의 해당 코드를 보고 든 의문의 해결https://hashcode.co.kr/questions/323/%EA%B0%80%EC%83%81-%EC%86%8C%EB%A9%B8%EC%9E%90%EB%8A%94-%EC%96%B4%EB%96%A4-%EA

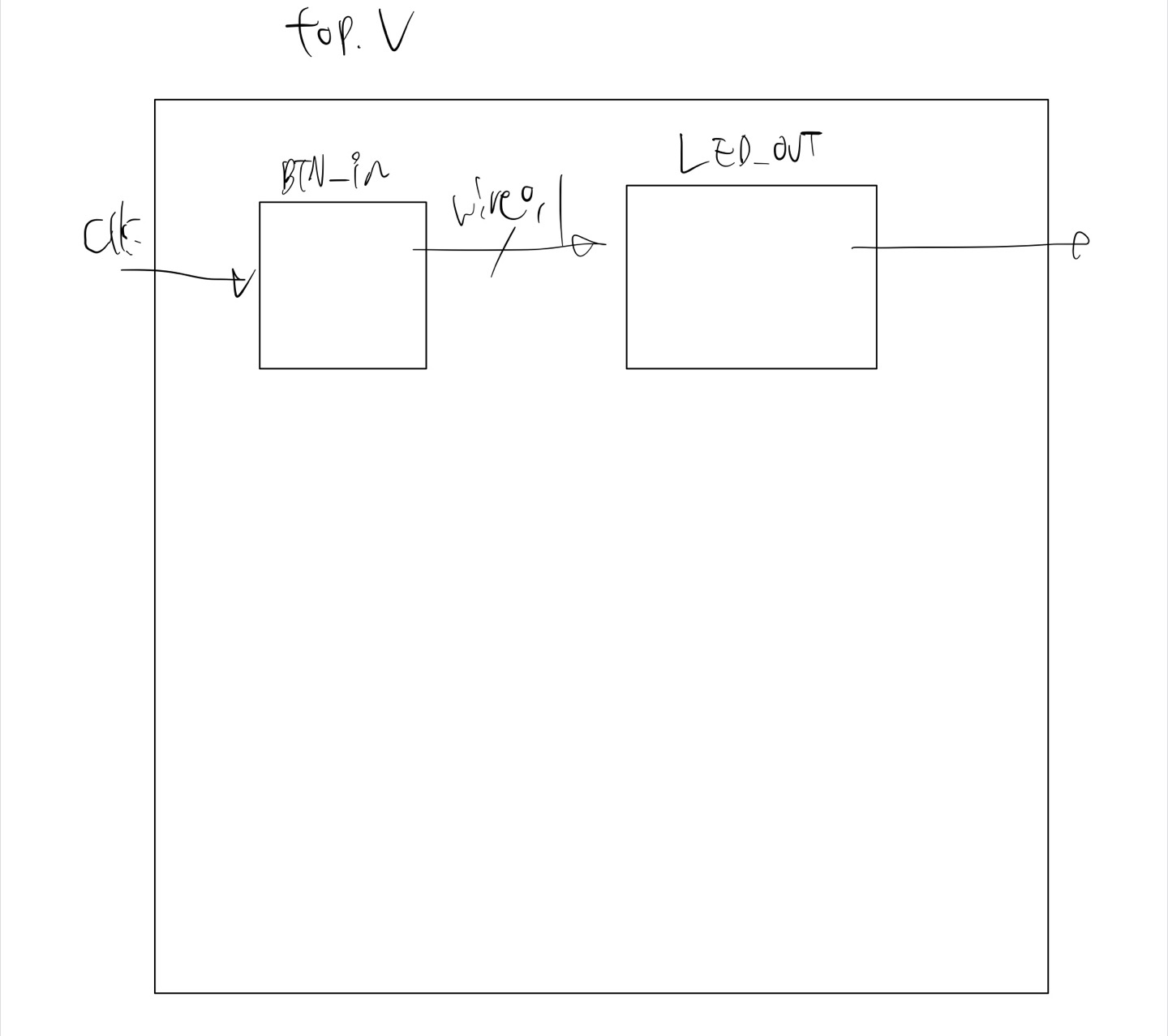

10.[Verilator] Verilator synthesizing multiple .v files with multiple modules

이제 여러 .v 파일의 여러 module 을 합성해볼 차례이다.이 다음부터는 Verilator 공식문서 정독포함 약 3시간의 삽질이 들었고, 그 결과 Verilator 에 대한 대략적인 감이 잡히게 되었다.그 삽질의 결과를 여기에 기록하고자 한다.여러 Verilog 파

11.[URP] AMBA 에 대하여

우수한 디지털회로 설계 엔지니어의 역량이 무엇이냐는 물음에 대한 답으로 블라인드에서 '여러 통신규격의 경험이 있는 사람' 이라는 답글을 보았다.내가 해본 것은, UART Rx Tx 구현 뿐이며, 이는 매우 간단했다.그러나 현업에서는 AMBA라는 것이 매우 널리 쓰인다는

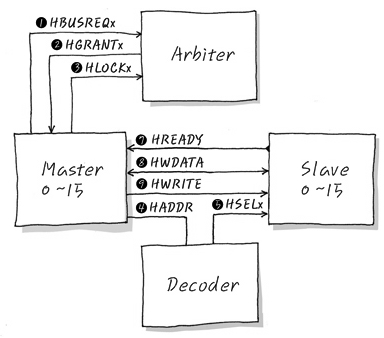

12.[URP] AMBA의 Arbiter란?

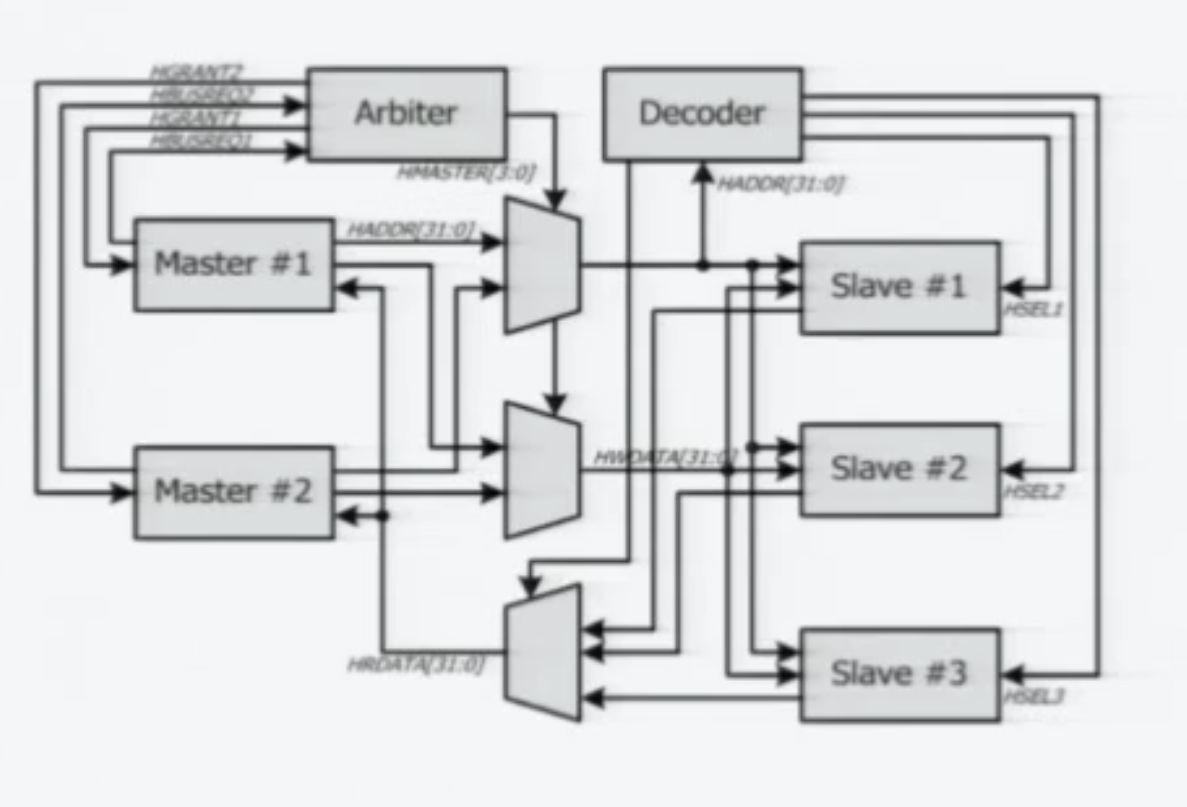

참고한 출처를 먼저 밝힙니다앞서 위와 같은 사진을 보았다.Arbiter는 버스 통제권을 쥐고 있는 놈으로써, 대빵 역할을 한다.Master와 Slave 는 AMBA System 상에서 최대 16개까지 붙을 수 있다고 한다. 따라서 0~15까지 있다.Decoder 는 M

13.[URP] IDEC AMBA 강의 필기 1

늘상 하듯 아이패드의 노타빌리티로 녹음동기화된 필기를 하려다가,AMBA의 경우 필기보다는 타이핑을 통한 저장이 더 유리할 듯 하여 Velog에 필기를 하도록 하였다.강의출처P.S. - 3년간 게임을 안하다가, 블루아카이브를 최근에 시작했는데, 그덕분에 3일을 정말 쓰레

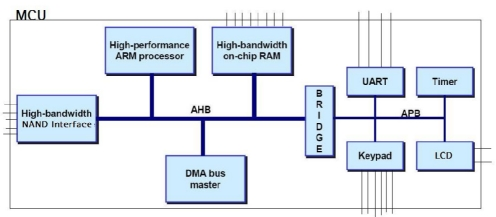

14.[IDEC] 디지털 SoC 설계 필기 1일차 1,2교시

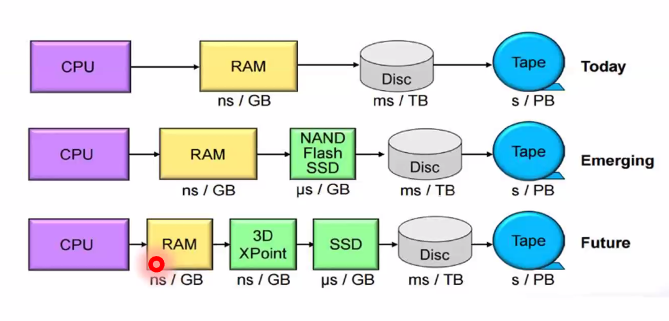

강의출처각 칩이 빠르다고 해도, 결국 스스로가 빠른만큼 끊임없이 자신이 연산한 결과를 보내야 하고 또 받아들여야 하기 때문에 통신의 발전과 연산의 발전은 서로 함께 이루어질 수밖에 없다.이에, 다양한 제조/개발사들에 의해 각 기기 또는 IP는 매우 다양한 종류가 난립할

15.[IDEC] 디지털 SoC 설계 필기 1일차 3,4교시

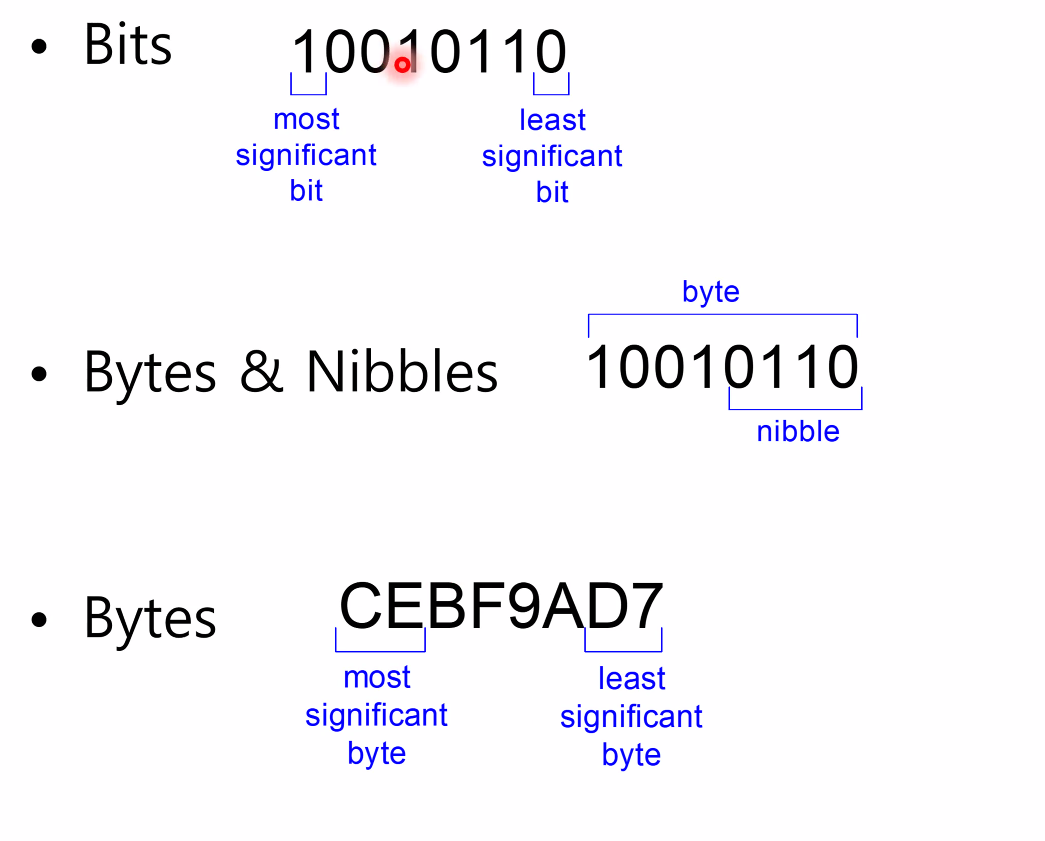

강의출처대략 학부2학년 수준의 강의이니 가볍게 들으면 될 것 같다.헷갈리면 안되는데, 가끔씩 헷갈려서 기재한다.16진법 알파벳 하나가 0.5바이트임에 유의중학교때 배울 이론.음수를 포기하는 대신, 가장 간단하다.논리회로 1학년때 배웠을 이론.MSB 1개를 sign 표기

16.[Verilog] modelsim 이모저모

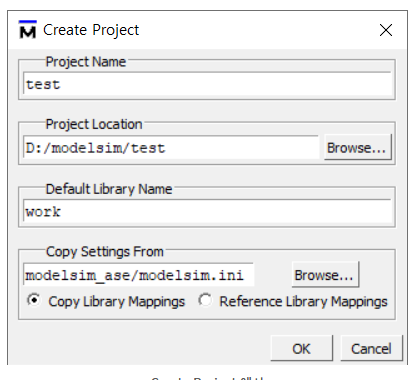

modelsim 1년쯤 전에 썼다보니 쓸 때마다 모든 것이 새로워서 삽질을 하게된다.이에 온라인 필기장을 만들고자 한다.modelsim 기초조작 잘 설명이 되어있는 블로그왠지는 모르겠는데 SSD인 D 드라이브에서 소스 끌어오니 안된다.C드라이브의 내 경우는C:\\int

17.[IDEC] 2017 AMBA AXI 기반 IP 설계와 검증 - 1-2

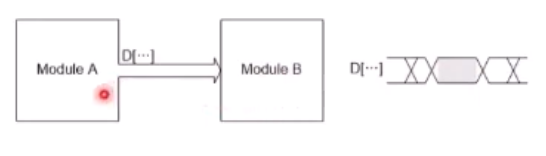

강의출처39m요즘의 버스는 전부 Synchronous이다.즉, 모든 동작이 하나의 클럭에 동기화되어 동작한다는 뜻이다.서로 다른 클럭을 가진 두 IP가 통신을 하게 되면 Clock Domain Crossing 이라고 한다.만일 Clock 동기화이지만, 어느정도의 Pha

18.[IDEC] 2017 AMBA AXI 기반 IP 설계와 검증 - 2-1: Introduction to AHB

강의출처본격적으로 AHB 의 설명에 들어간다.HCLK for AHBPCLK for APBBCLK for ASBA~ for unidirectional signal between MASTER <-> ARBITER for ASBex) AGNTx, AREQxD~ for

19.[IDEC] 2017 AMBA AXI 기반 IP 설계와 검증 - 2-2, 2-3: AMBA 5 AHB 5

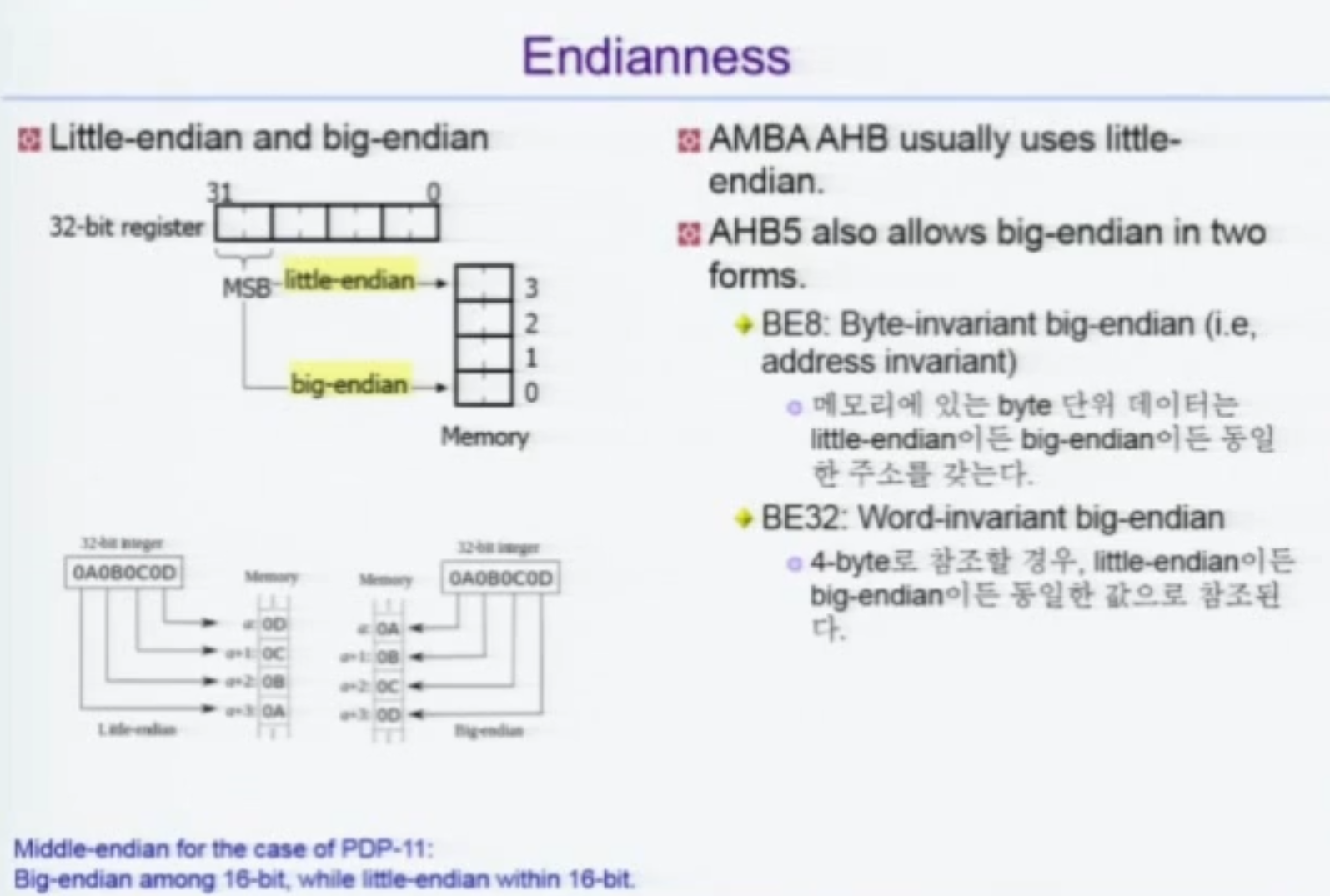

강의출처질문)슬레이브마다 HREADYin out 모두 있는데, 대표성이 있는 값을 중재하는 부분이 누구인가? 마스터인가 아비터인가 디코더인가?답) 마스터는 HREADY 를 반드시 봐야하고, 슬레이브는 당연히 HREADY를 출력할 것. 이 때, 슬레이브는 모든 HREAD

20.선행연구시 심득사항

출처: 논문작성길라잡이 - 선행연구조사선행연구조사논문을 쓸 때 가장 먼저 하는 작업 중 하나가 주제 관련 선행 연구를 조사하는 일입니다.선행연구란 연구와 관련한 개념들이나, 개념들 간의 관계에 대한 설명을 담은 연구 입니다.논문에 필요한 개념들에 직접적으로 관련된 설명