서론

우수한 디지털회로 설계 엔지니어의 역량이 무엇이냐는 물음에 대한 답으로 블라인드에서 '여러 통신규격의 경험이 있는 사람' 이라는 답글을 보았다.

내가 해본 것은, FPGA<->PC간 UART Rx Tx 구현 뿐이며, 이는 매우 간단했다.

그러나 현업에서는 AMBA라는 것이 매우 널리 쓰인다는 것을 풍문으로 들어서 알고만 있는 상황이었다.

그러던 와중, URP 주제로 선정이 된 것이 AMBA다.

약 1시간 내로 텍스트 정독을 통한 AMBA 에 대한 감을 정립하고 난 뒤,

IDEC의 기안도 박사 강의를 시청하여 AMBA 에 대한 이해를 하고

URP 1주차 과제로 나온 AMBA AHB Slave RTL 구현의 초석으로 삼고자 한다.

참고사이트1

참고사이트2

참고사이트3

참고강의1

참고강의2

AMBA란?

SoC 칩 내부에 IP들이 여러 개 있을 것이다.(Intellectual Property)

그 IP들간에 소통의 규격이 난잡하면 당연히 좋지 못하다.

유지보수에도 좋지않고, 개발과정에서 불필요한 자잘한 명세에 관한 타협이 추가로 요구되어버리기 때문이다.

따라서, ARM은 Advanced Microcontroller Bus Architecture 라는 SoC Target On-chip Bus Protocol 을 개발하여 ARM이 주도하는 IP간 통신규격을 정의하고 공개하였다.

Bus란 무엇이 요구되는가?

가장 근원적인 물음.

Bus는 무엇을 해야할까? 뭘 전송해야할까?

크게 3가지이다.

1. Address

2. Data

3. Control Signal

컴구개에서 배웠겠지만, 크게 컴퓨터의 Path는 DataPath와 ControlPath 로 나뉜다. 거기에 Address를 따로 분리시킨 것이다. 내 추정이긴 하지만 관점에 따라 Address는 Data Signal 의 일종으로 분류할 수 있을 것이다

AMBA의 종류

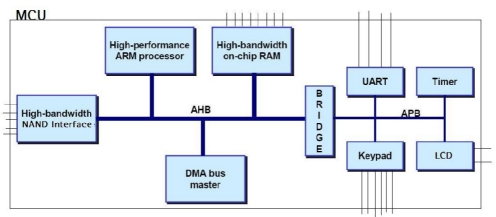

어쨌든, AMBA는 매우 유명한 아래 그림과 같은 Schematic 을 띤다.

AMBA는 3가지 Protocol을 정해놓았고,

그것은 AHB/APB/ASB이다.

(AHB Bus라고 하면, AHB Protocol을 지원하는 Bus interface 에 물린 Bus 라고 해석하면 된다.

뭐 Bus 자체는 단순한 구리선에 불과할테니 당연한가.)

AHB

Advanced High performance Bus 이다.

ASB를 대체하였으며, 데이터버스이다보니 굵은 선(대용량버스) 인 것을 볼 수 있으며, APB와 Bridge로 구분된다.

Bridge 는 서로다른 두 규격의 도란스 역할을 수행하는 IP 라고 이해하고 있다.

APB

Advanced Peripheral Bus이다.

주변장치의 경우 AHB만큼 고처리율의 버스가 될 필요는 없으므로 얇은 선인 것을 볼 수 있다.

ASB

Advanced System Bus이다.

원래는 AHB의 역할을 하다가, 고성능을 위해 AHB로 대체되었다는 수준으로 이해를 하고 있다.

AXI

Advanced eXtensivle Interface 라고 하는데,

AXI 는 Burst 기반이고

Write Response Channel 이 추가되었으며

Read Write 가 동시에 가능하고

시작주소만 가지고 Burst Transfer 가 가능한 갓-규격인 모양이다.

이 고속동작용 Bus는 나름 최신인지, ARM11 이상 Core 를 탑재한 MCU의 backbone bus 로 사용되고 있다고 한다.

이런 AMBA System 이 있는 덕분에 SoC 엔지니어들은 IP를 갖다끼울 때 매우 편하게 SoC를 확장할 수 있다고 한다.

AXI-Stream

아직 잘 모르겠다.

물음: 왜 Protocol 종류를 구분해놓았을까?

그 답은 효율성이다.

AHB는 APB보다 훨씬 빠르니까, 모든 IP를 AHB로 연결하면 안되냐는 물음은 당연하다.

그 경우, 빠른 IP끼리 서로 통신을 하다가 중간의 저속 IP에게 뭔가 부탁할 일이 생긴다면 뭐 어디에 Context Switch 마냥 맥락을 저장하고 다른 짓을 하는 Scheduling 이라도 하지 않는 이상, 그대로 Waiting 해야하는 문제가 생길 것이다.

따라서, 빠른 놈은 빠른 놈끼리, 느린 놈은 느린 놈끼리 모아두는게 낫다.

AMBA의 경우 Bridge 의 도입으로 이를 구현하였다.

빠른 IP가 열일을 하다가, 주변장치에 보낼 상호작용이 있으면 그저 Bridge 에 넘기고, 자신은 할일을 한다.

다시 Bridge로부터 회신이 돌아오면 그 때 Context Switch마냥 되는 모양이다. Context Switch(?)에 필요한 정보는 애초에 Bridge에서 전부 종합을 해서 주겠지.

어쨌든, 이러한 연유다.

ASB(구) VS AHB(신)

원래 AMBA에는 ASB와 APB만 있었다.

AMBA도 진화해야하므로, Multiplex Bus 기반의 AHB를 개발했다.

Multiplex Bus란?

Bus가 Address Line 과 Data Line과 Control Line 모두 공유를 한다는 뜻이다.

(Bus에 Address Line 과 Data Line과 Control Line 모두 포함이 되어있다는 뜻으로 이해했다.)

작동방식

처음에 주소를 먼저 쏜다.

그 뒤, 데이터를 Burst하게 쏜다.

그것이 AHB이다.

그래서 ASB와 AHB의 차이가 뭐냐고?

ASB는 이와 달리, 주소/제어/데이터라인이 모두 분리되어있는 양방향 Bus 구조이다.

구조상 Address와 Data를 번갈아주며 쏴주도록 Design 되어있기 때문에 Burst하게 Data를 날리기 어렵다는 단점이 있고 이는 Throughput 저하로 직결된다.

(아니 Address Line 과 Data Line 분리되어있다며? 근데 왜 번갈아주며 쏘도록 Design한거야?)

AHB와 ASB면 끝나냐?

당연히 아니다.

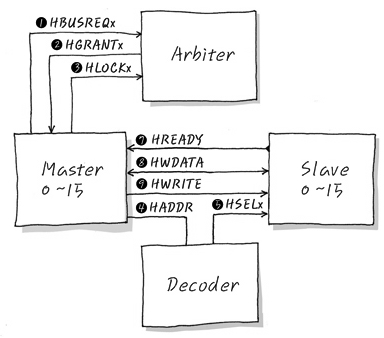

AMBA Bus System 을 구성하는 요소에는 HW IP와 Decoder 가 있고,

각 IP의 관계는 Master 또는 Slave 가 된다.

- Master: Slave에게 Read Write 요청 가능

- Slave: 요청받은대로 R W 작업 직접 수행, 그 뒤 그 명령에 대한 성공/실패/Waiting 등의 상태를 다시 Master측에 report함.

인문학적으로 말하면, Master는 Bus를 사용하고자 하는 주체이다. Bus를 사용한다는 뜻은 Bus에 데이터를 흘려보낸다는 뜻이다.

Slave는 그것을 받아 그저 일을 하는 노예다.

Master와 Slave 만 있다고 통신이 가능하냐?

당연히 아니다.

Master 와 Slave 의 통신을 위한 복잡한 Bus System 이라는 것이 있다.

이 Bus System 을 정리할 신호등이 필요한데,

이 신호등을 Arbiter 라고 한다.

얘 아니다.

- Arbiter: Bus를 누가 쓸 것인지에 대한 결정권을 가진다.

즉 Arbiter 에게 허락 못받으면 Bus 못쓴다.

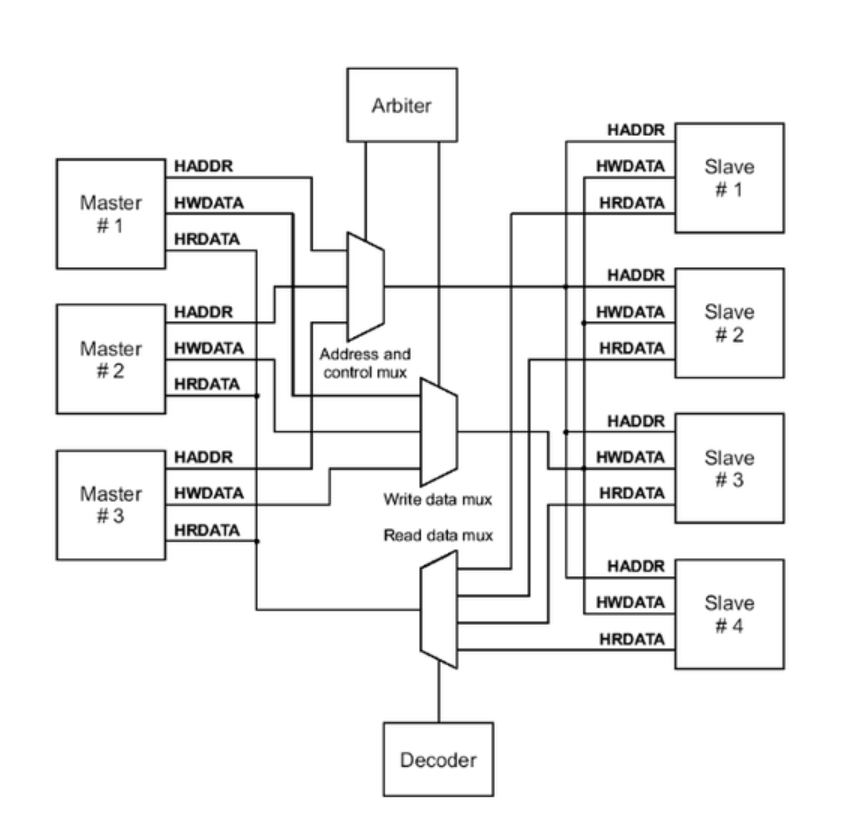

모든 통신은 간단히 모식하면 아래 Schematic과 같다.

이 구조는 AMBA 뿐만 아니라 Memory Control, Peripheral Device Control, 대략 비슷비슷하다고 한다.

좀 더 구체적으로 표현한다면 아래와 같다.

다음 포스트에서 아비터에 대한 자세한 설명을 이어가도록 한다.

안녕하세요! 후배입니다.. 너무 옛날이라 기억이 잘 안나시겠지만 혹시 실례가 안된다면 어느교수님에게서 urp 하셨는지 여쭤봐도 될까요?