그래서, 앞 포스트의 그 그림을 설명해봐라!

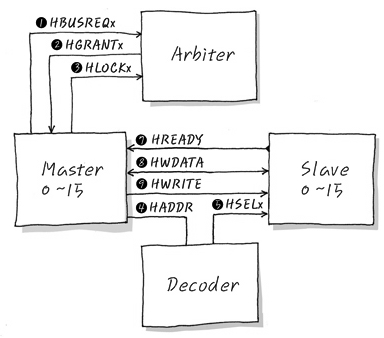

앞서 위와 같은 사진을 보았다.

Arbiter는 버스 통제권을 쥐고 있는 놈으로써, 대빵 역할을 한다.

Master와 Slave 는 AMBA System 상에서 최대 16개까지 붙을 수 있다고 한다. 따라서 0~15까지 있다.

그럼 Decoder 는 뭐하는 놈인데?

Decoder 는 Master 와 Slave 의 길을 제대로 뚫어주는 놈이다.

Master가 접근하고자하는 주소를 미리 받고,

Slave에게 "야~ 너한테 일감 간단다~ 준비해라~" 라고 알려준다.

각 신호 뒤의 x 첨자는 0~15 숫자가 들어감을 의미한다.

즉 여러 겹의 선이 있는 전선이라는 말이다.

AMBA 사용순서

- Master->Arbiter: HBUSREQ

"아비터야, 나 지금 버스 써도 되니?" - Arbiter->Master: HGRANT

"비어있네. 써라" - Master->Arbiter: HLOCKx

"아비터야 그럼 x번 내가 쓴다~"

Arbiter: 'x번...마스터가...사용...중...메...모... ㅇㅋ.

이제 딴 눈치없는 Master가 HBUSREQ 날리면 내가 책임지고 빠꾸맥여줄게'

=>(생략되었는데, 만약, 동시에 요청이 날아오면 Priority를 체크한 뒤 버스허가권을 날려준다) - Master->Decoder: HADDR

"이 주소로 접근하고자 하는데, Decoder야 Slave좀 준비시켜주라" - Decoder->Slave: HSELx

"x번 Slave 아쎄이 대기!" => Slave 동작 활성화 - Master->Slave: HWRITE HIGH(==WRITE), if LOW==READ

"Slave야 Write한다?" - Slave->Master: HREADY

"준비완료" - Master->Slave: HWDATA

"Data 넣을게."

※참고로, Read활때도 동일한 HWDATA 버스 사용

Transaction

Transaction은 Bus를 쓰는 동안에 Data를 주고받는 것을 의미한다.

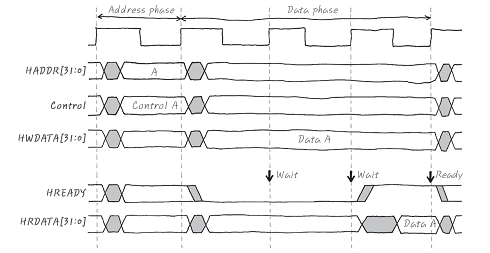

여기서, 6~8 사이의 Timing Diagram 은 아래 사진과 같다.

- Address Phase: 주소를 날리는 과정(시간)

- Data Phase: 데이터를 날리는 과정(시간)

- wait: Slave는 보통 Master보다 느린 경우가 많은데, "호에엥 저 아직 준비 안되었어오..." 라는 의미로 HREADY 신호를 LOW 로 Master 에 보내는 것이다.

- wait state: 말그대로 wait 상태인데, 이 기간동안 준비가 미비된 Slave는 준비동작을 한다. Master는 기다리는 모양이다.

(그런데 그 현상을 막으려고 Bridge 를 두고 APB, AHB 분리한거 아니었나? 이건 AHB 내부의 현상인가?)

Control Signal이 HWRITE 뿐이냐?

위 그림에서는 Control Signal 이 HWRITE 뿐인데,

사실은 HTRANS[1:0], HBURST[2:0], control pin, 등등 많다. 이들은 Burst Transfer 를 어떻게 할건지를 의미한다.

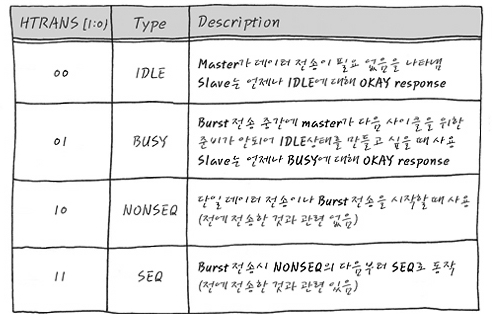

HTRANS[1:0]

왜 이렇게 만들었나?

Continuous 한 Address 의 Data 를 Burst하게 전송할 때 매우 유용하기 때문이다.

우리는 이를 Burst Transfer 라고 부른다.

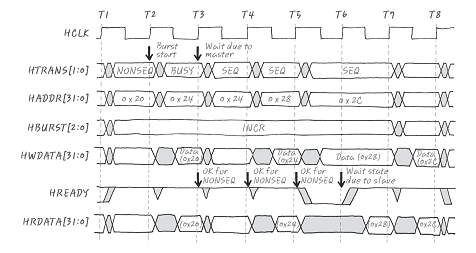

아래에 Time Diagram 이 있다.

Data를 보내는 HADDR이 0x20~0x2C까지 연속적이다.

그렇다면 HADDR 시작 0x20 을 보냄과 함께 HTRANS는 NONSEQ 신호를 보낸다.

그 뒤, HTARNS는 BUSY 를 한 번 때리고

그 뒤에는 wait 이 아니라면 SEQ와 주소가 알아서 늘어나면서 계속 연달아 날리게 된다.

Slave가 wait! wait! wait! 하면 Master 는 기다려주는데, Busy는 Master가 바쁠 때 Slave 에게 보내는 비슷한 개념이라고 보면 될 것 같다. Master라고 바쁘지 말란 법 없으니.

그래서 BURST TRANSFER 의 장점이 뭔데?

임베설시간에 Burst 한 Write 는 카메라 연속속사 등과 같은 기술에 필수적으로 처리해야하는 issue 라고 들었는데, 조금 다른 맥락일 수 있겠다.

본론으로, Burst Transfer 의 장점은

원래 한 번 쓰려면 하나의 Address Phase + Data Phase 를 따로 가져야 Transaction 이 완성되는데

연속주소라면 하나 이상의 연속된 Data 임이 보장되었으므로 무지성으로 쫘르륵 써주기만 하면 된다.

※보통 NOR메모리의 경우 Burst Mode 가 있는데, 이걸 쓰면 연속주소의 경우 하위 Address pin 만 변하는 특징이 있으므로 하위주소만 변동시켜주면 알아서 Data가 연속적으로 읽히는 장점이 있다.

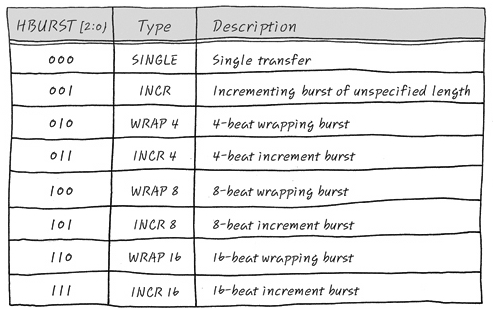

HBURST[2:0]

위 그림의 HBURST 의 INCR 라고 된 부분은 뭘 의미할까?

생각해보면 당연하다.

얼마나 묵시적으로 address 점프를 뛰어가며 burst transfer 할 것인지를 표시해줘야할 것 아닌가.

아키텍쳐마다, 상황마다 사용하는 자료형의 크기가 다를테니 말이다.

INCR과 WARP 두 가지 계열이 있음을 확인할 수 있다.

WRAP 은 뒤에 붙은 숫자가 Address Boundary이다.

INCR 또한 뒤에 붙은 숫자가 Address Boundary이다.

Address Boundary는 "이 범위 안에서만 Burst를 할 수 있다"는 것을 의미하며 일종의 "보폭"이다.

WRAP/INCR 뒤에 붙은 숫자는 "해당 배수의 주소만큼 boundary 를 이룰 수 있으며 그 범위 안에서만 Burst를 할 수 있다" 라는 것을 의미한다.

그래서 WRAP이랑 INCR 차이가 뭔데?

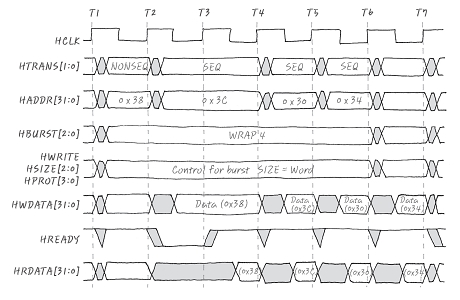

예시 사진을 보자.

HSIZE를 보니 Word다.

이 때, WRAP4이므로

Word 4개씩 Burst 되는 것이다.

32bit ARM에서의 WORD는 4Byte*4 == 16Byte == 0x10 Byte 이다. 그게 보폭이다. 경계주소는 보폭의 배수가 되어야 한다.

0x38이 초탄으로 박혔으니, 0x30보다 크고 0x40 보다 작은 것이 해당되는 범위가 될 것이다.

4-Beat Wrapping Burst 이므로 다시한번 보면

0x38 다음에 0x3C 다음에 0x40 로 안가고 0x30 0x34 로 돌아왔다.

이렇게, 주소가 Wrapping 되어 그 내부에서만 Burst로 사용된다.

이게 WRAP이다.

당연히, 이런 알고리즘이므로 Wrap Type의 Burst를 사용할 때 Random 주소로부터 시작하면 상당히 골때리는 상황이 벌어질 것이다. 참조한 블로거의 말로는, 여태 WRAP 사용한 사례를 보지 못했다고 한다(그럼 왜 개발한거야).

INCR는 그럼?

INCR 는 무지성 ++시켜준다고 보면 된다.

Burst 횟수에 따라 무지성 증가한다.

0x30 0x34 0x38 0x3C 이렇게 계속 커진다.

(그럼 0x40을 초과할 수도 있다는건가? 그럼 Address "Boundary" 라는 말의 의미가 무색해지지 않나..?)

Control Pin

일단 있다는것만 인지하고 넘어간다.

주저리

AHB, ASB, APB 외에 AMBA 3.0 Spec 에 새로 추가된 AXI도 있다고 한다.

Advanced eXtensivle Interface 라고 하는데,

AXI 는 Burst 기반이고

Write Response Channel 이 추가되었으며

Read Write 가 동시에 가능하고

시작주소만 가지고 Burst Transfer 가 가능한 갓-규격인 모양이다.

이 고속동작용 Bus는 나름 최신인지, ARM11 이상 Core 를 탑재한 MCU의 backbone bus 로 사용되고 있다고 한다.

이런 AMBA System 이 있는 덕분에 SoC 엔지니어들은 IP를 갖다끼울 때 매우 편하게 SoC를 확장할 수 있다고 한다.