- 전체보기(153)

- Parallelism(1)

- Power and Energy(1)

- test(1)

- Dependability(1)

- uart(1)

- I2C(1)

- casez(1)

- computer architecture(1)

- systemverilog(1)

- Reducing power(1)

- driver(1)

- agent(1)

- Performance(1)

- VIF(1)

- build_phase()(1)

- convert2string()(1)

- {32{sub}}(1)

- Cost of IC(1)

- flynn's Taxonomy(1)

- casex(1)

- uvm_do(1)

- type_id::create(1)

- 삼항연산자(1)

- uvm_info(1)

- Static power(1)

- monitor(1)

- Constructor(1)

- spi(1)

- Model Compression(1)

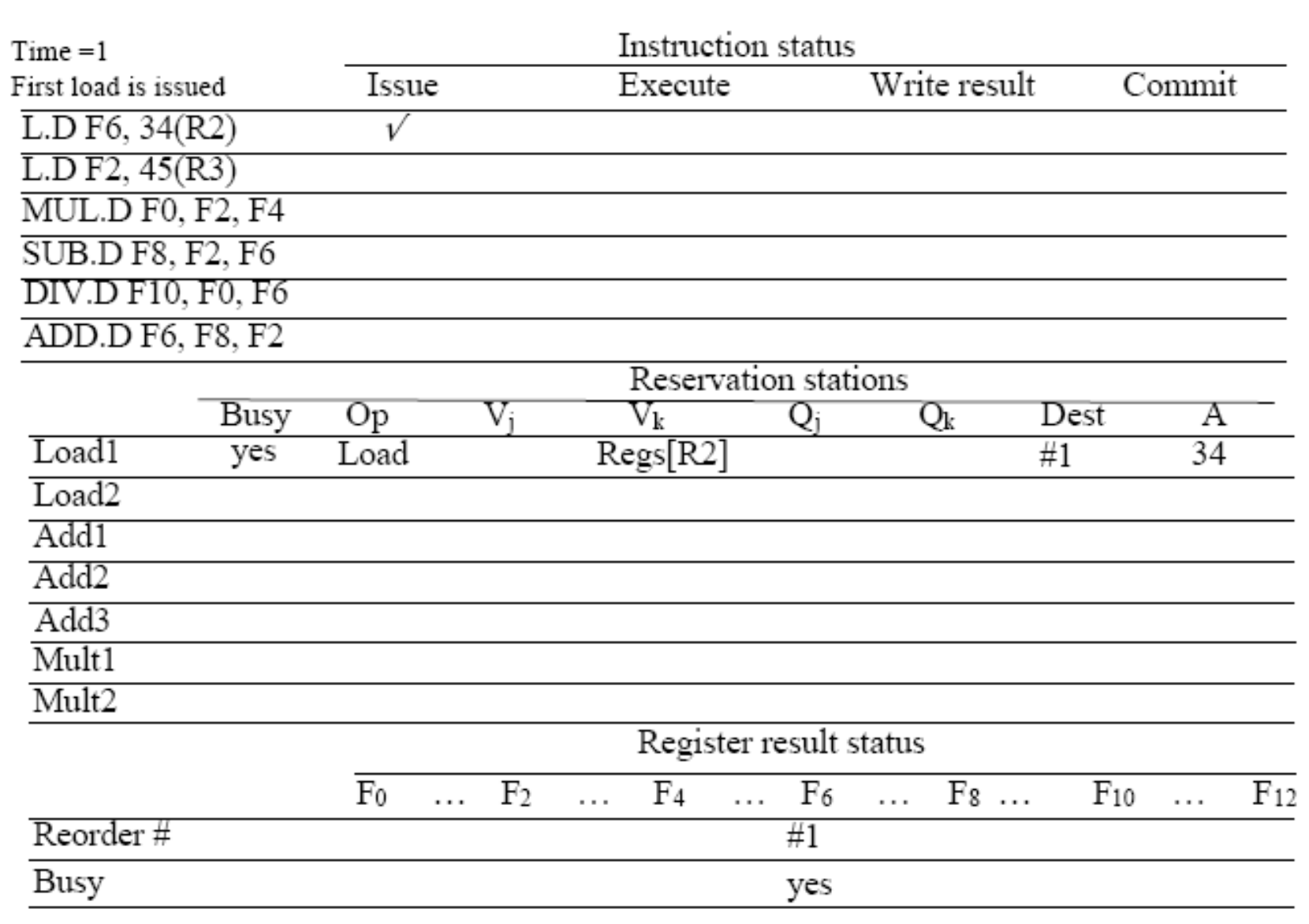

Hardware-based speculation

한 사이클에 명령어를 4개, 8개씩 빨아들이는(Fetch) 슈퍼스칼라 구조에서는 단순히 분기 방향 하나 맞췄다고 파이프라인이 매끄럽게 돌아가지 않습니다. 명령어들 사이에 얽혀있는 데이터 의존성(Data Hazard) 때문에 ALU가 놀고 있는 시간이 생기기 때문입니다.

Cyber HW 5

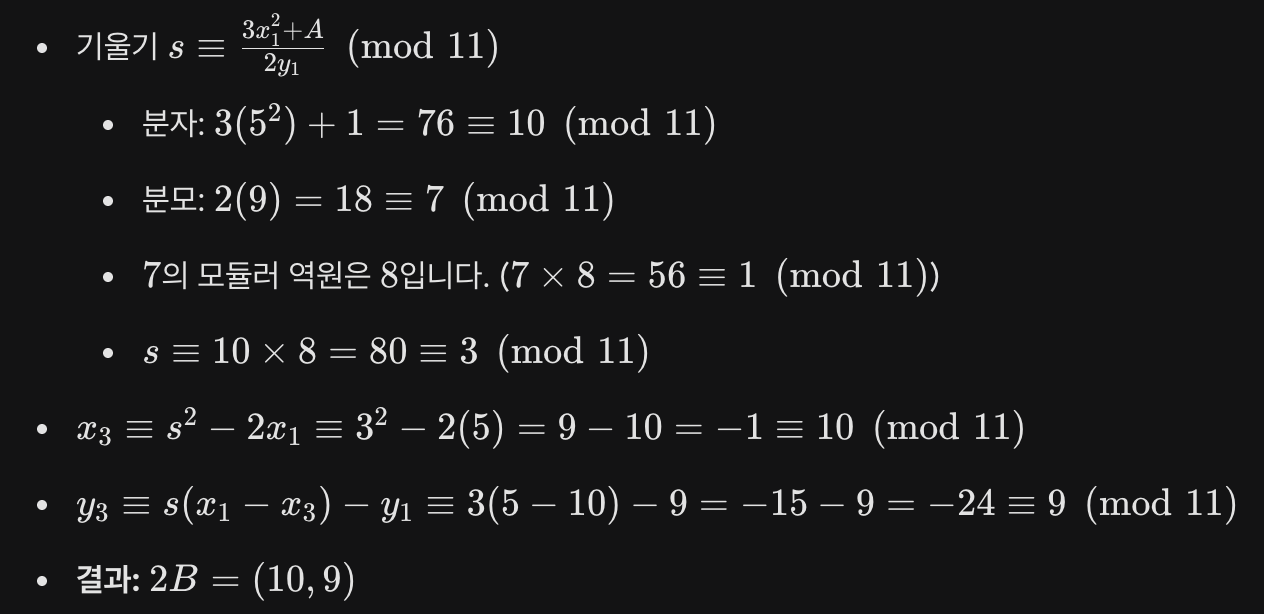

개인 키 $a = 6$상대방의 공개 키 $B = (5, 9)$타원 곡선 $E: y^2 \\equiv x^3 + x + 6 \\pmod{11}$ (즉, $A = 1, B\_{curve} = 6, p = 11$) $B \\rightarrow 2B \\rightarrow 3

Trouble shooting

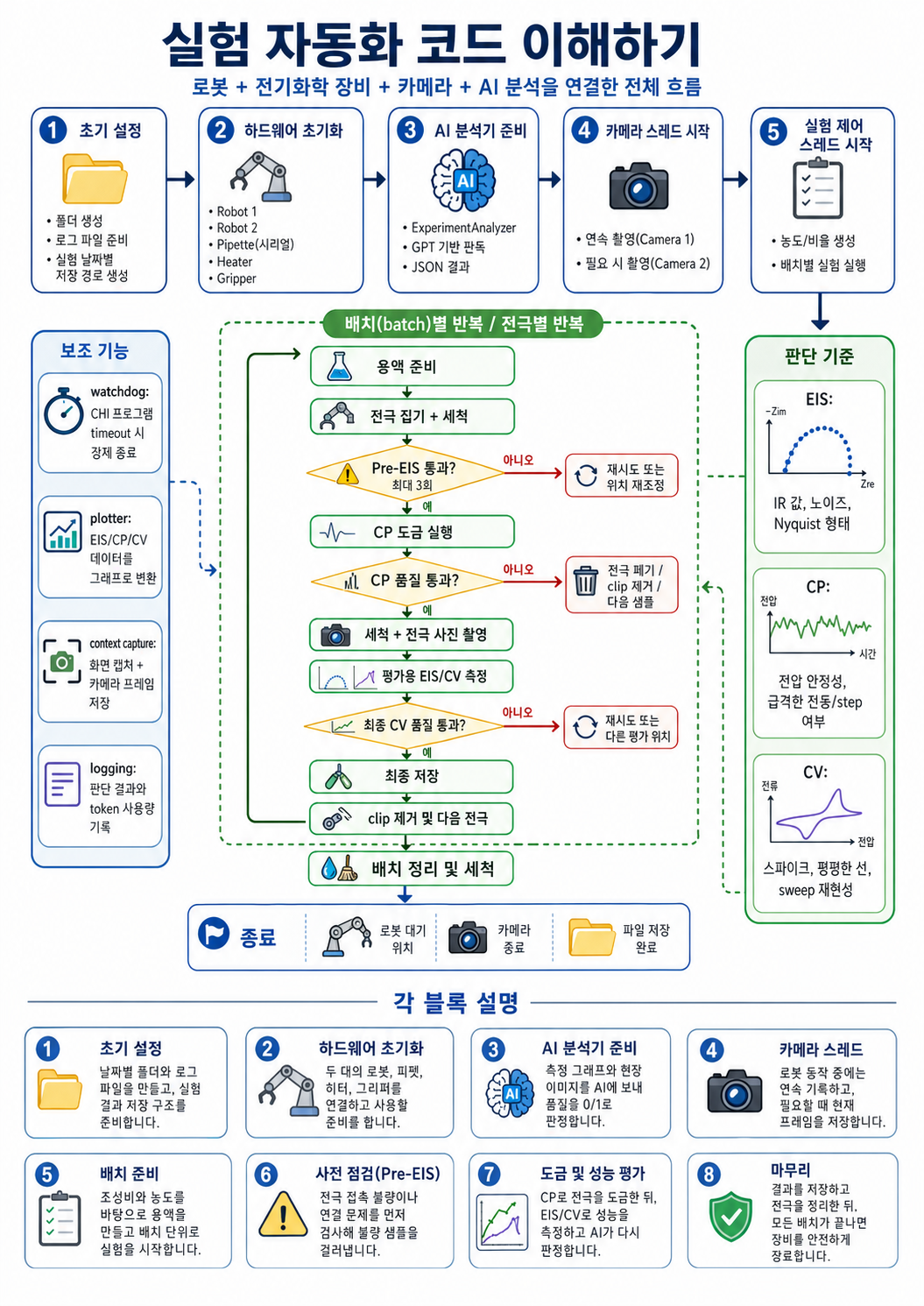

이 세 가지만 통제할 수 있으면 로봇 팔의 모든 물리적 움직임을 지배할 수 있습니다.마스터 명령어 (move_to_tube 함수):로봇 팔의 이동, 주사기(펌프) 제어, 집게(Gripper) 개폐, 측정 장비(CHI) 호출을 모두 관장하는 만능 함수입니다. 로봇을 움직

chi(case) 함수의 8가지 동작 모드 해부

: CP (Chronopotentiometry, 정전류 인가)물리적 동작: 정전류원(Current Source) 모드입니다. -0.004A(-4mA)의 직류 전류를 1200초(20분) 동안 강제로 밀어 넣습니다.목적: 쌩 철망에 Ni, Mo, P 이온을 억지로 달라붙게

기본 코드지식

Communication Specs: What are the physical interfaces (UART, TCP/IP) and specific port settings (baud rate, COM port) connecting the main PC to the ro

배경지식

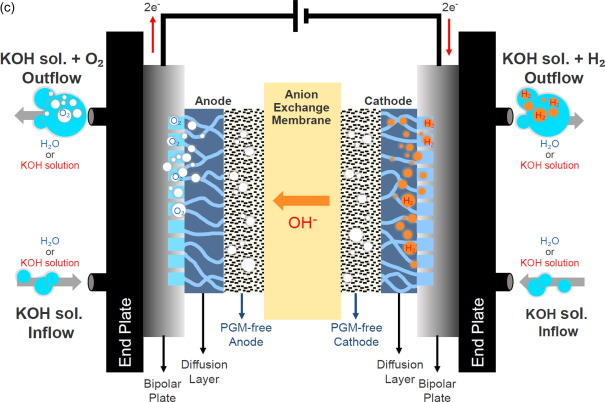

수소 = 궁극의 '무한 용량 하드디스크'여기서 수소(H2)가 등장합니다. 수소를 자체적인 연료라기보다는 '남는 전기를 보관하는 화학적 에너지 저장 매체(Energy Carrier)'로 이해하셔야 합니다.Write (저장): 낮에 남아도는 잉여 전력으로 물(H2O)을 전

NiMoP electrodeposition for water splitting

수소 = 궁극의 '무한 용량 하드디스크'여기서 수소(H2)가 등장합니다. 수소를 자체적인 연료라기보다는 '남는 전기를 보관하는 화학적 에너지 저장 매체(Energy Carrier)'로 이해하셔야 합니다.Write (저장): 낮에 남아도는 잉여 전력으로 물(H2O)을 전

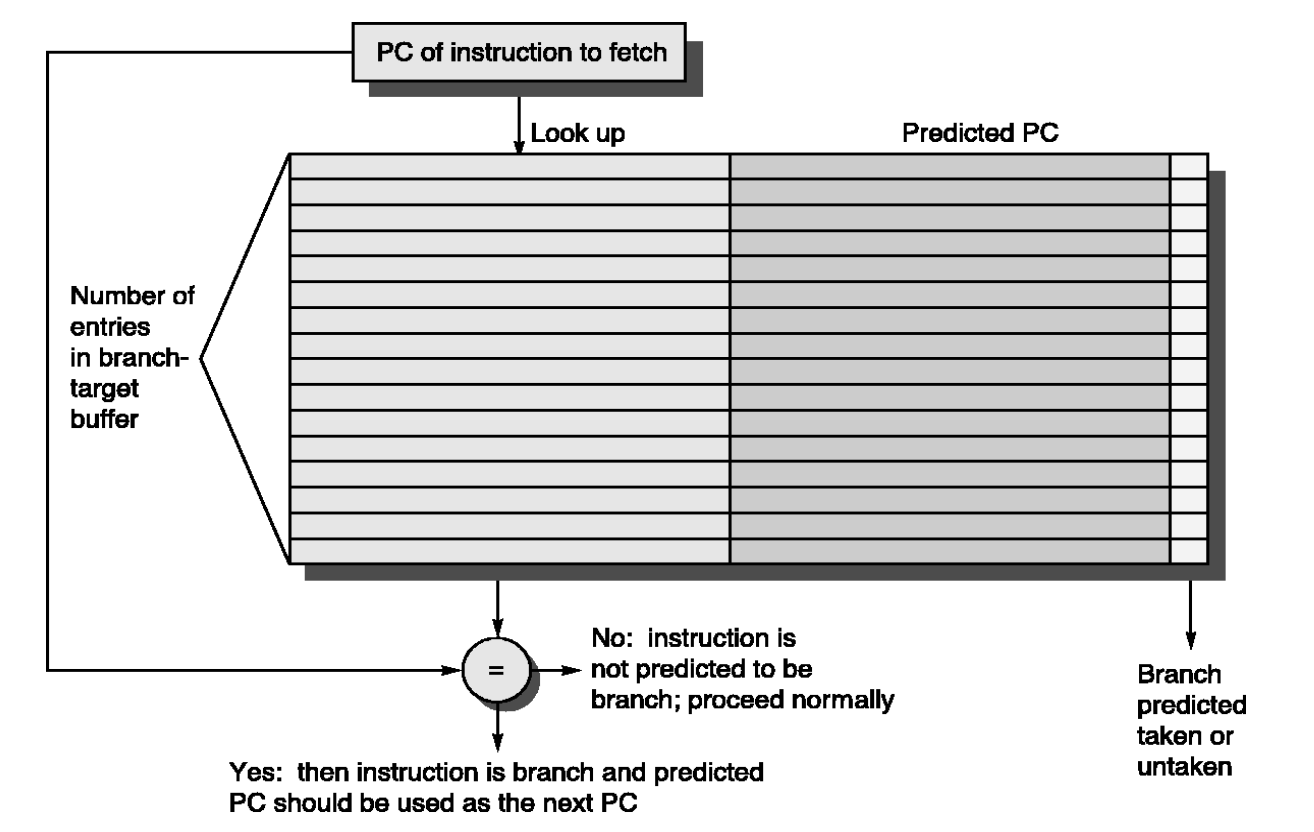

Tournament Predictors, Branch-Target Buffers (BTB)

\*Tournament Predictor (토너먼트 예측기)는 말 그대로 칩 내부에서 두 개의 서로 다른 예측기를 경쟁시켜서, "지금 이 분기문에서는 누구 말을 듣는 게 더 정확할까?"를 하드웨어가 스스로 판단하고 선택하는 메타 예측기(Meta-Predictor)\*\

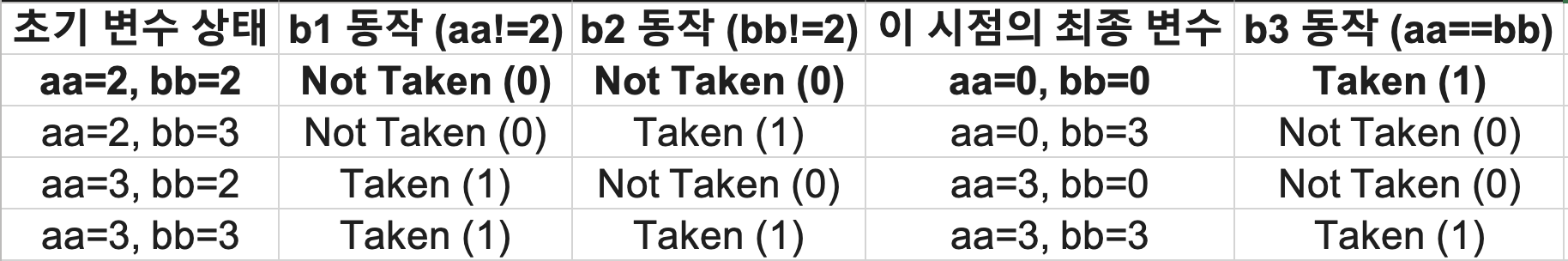

Correlated Prediction/ final --

핵심은 "서로 관련이 없어 보이는 앞선 두 개의 if문이, 세 번째 if문의 결과를 100% 결정지어 버린다"는 것을 증명하는 것입니다. 이것이 바로 주변 문맥을 파악하는 상관 예측(Correlated Prediction)의 존재 이유입니다.먼저 C 코드를 논리적으로

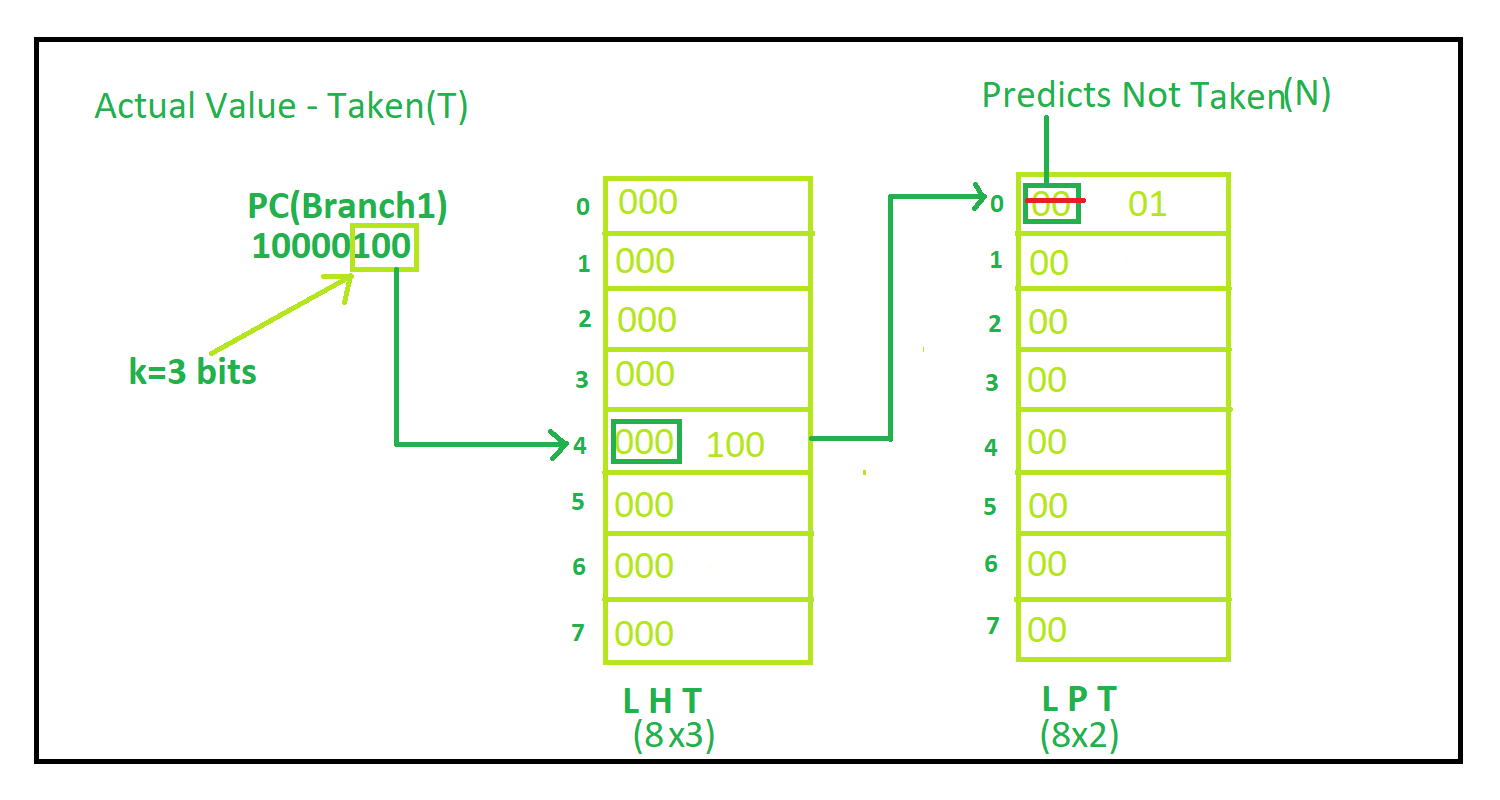

Dynamic Branch Prediction

Local Branch prediction:use own historyGlobal Branch prediction:determined by other instructionuse someone else history(동적 분기 예측의 필요성)파이프라인이 왜 과거의 기록을

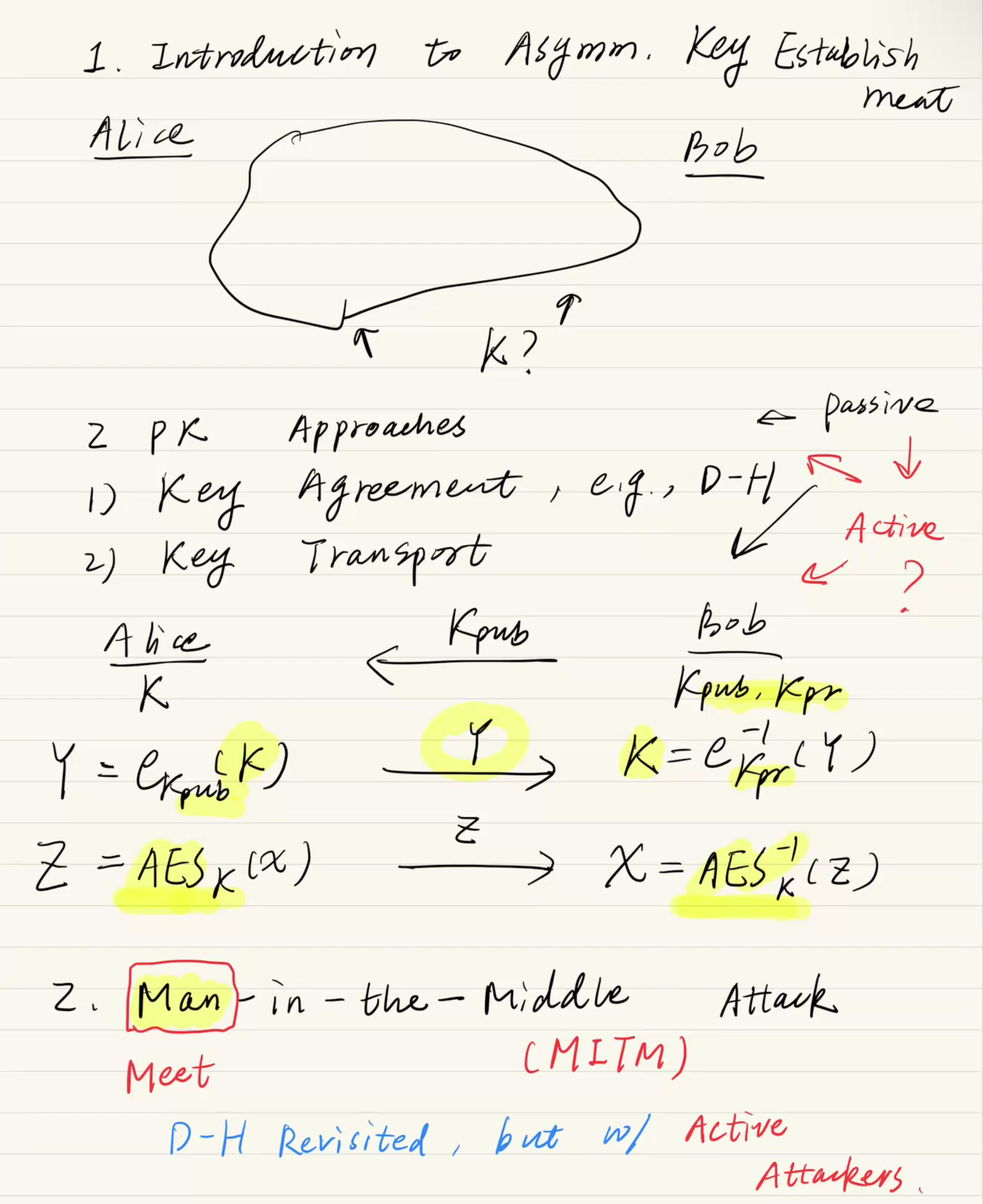

Man-in-the-Middle Attack(MITM), CA

KDC (Key Distribution Center)

MAC, HMAC, Markle-Damgord construction

MAC을 구현하는 방법 중 하나로, 방금 전까지 뼈빠지게 배운 해시 함수를 재활용하여 MAC을 만드는 방식입니다.요구 조건: 해시 함수처럼 입력 길이는 자유롭고(Arbitrary), 출력 길이는 고정(Fixed)되어야 합니다.HMAC의 기본 아이디어:새로운 암호 알고리

Shallow Copy vs Deep Copy

개념: 시스템 베릴로그에서 객체는 항상 핸들(Handle, 포인터와 유사) 형태로 존재합니다. 얕은 복사는 객체 내부의 알맹이가 아니라, 이 핸들의 주소값만 복사하는 것을 의미합니다.치명적 결과: 원본 객체와 복사된 객체가 메모리 상의 동일한 하위 객체(Nested o

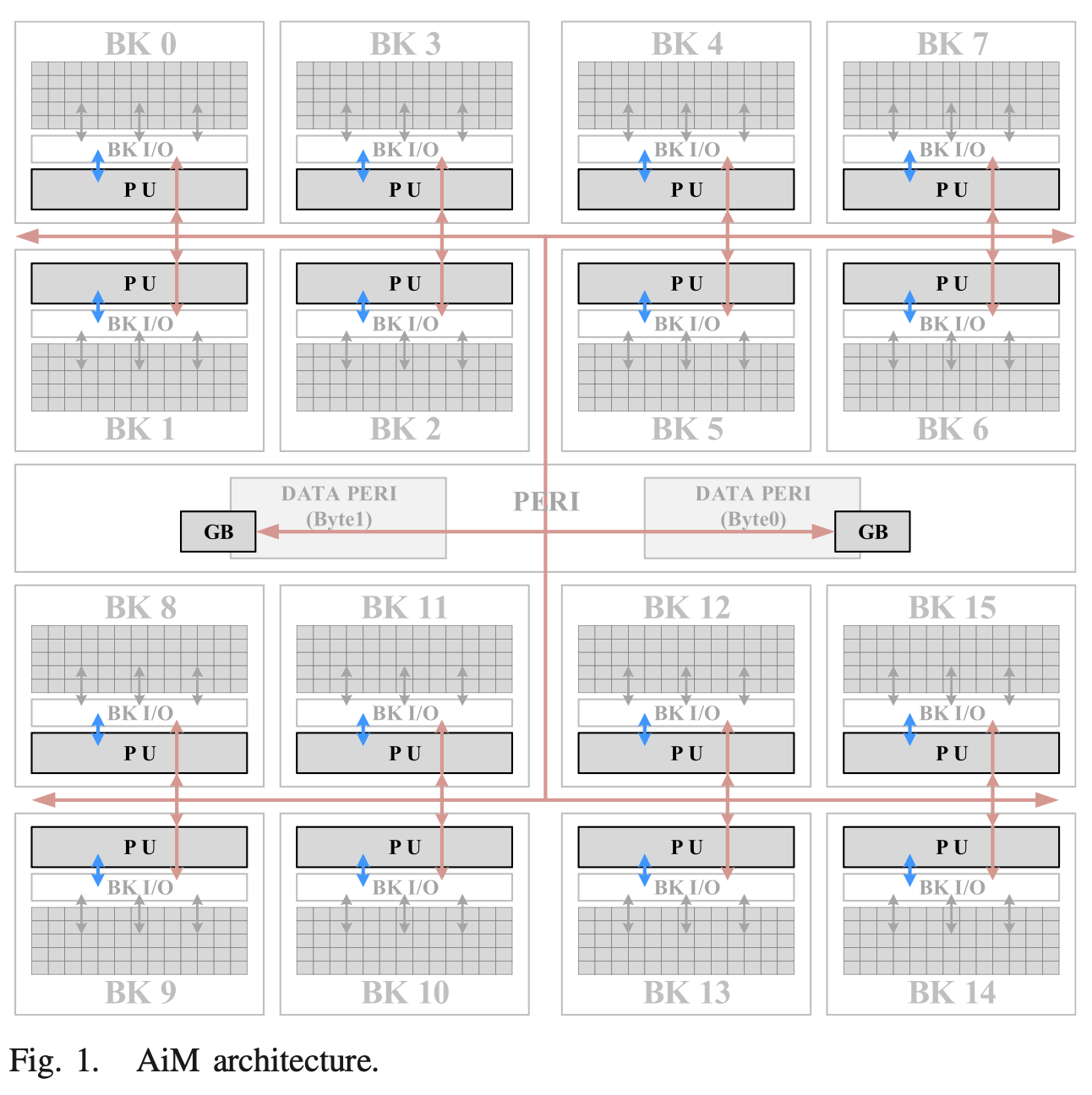

GDDR6 AiM (SK Hynix)

삼성 논문이 "최고 성능의 HBM에 PIM을 결합하자"는 하이엔드 전략이었다면, 이 하이닉스 논문의 핵심은 "HBM은 TSV(실리콘 관통 전극) 공정 때문에 단가가 너무 비싸니, 그래픽 카드에 널리 쓰이는 가성비 좋은 GDDR6에 PIM을 이식해서 대중적인 AI 가속기

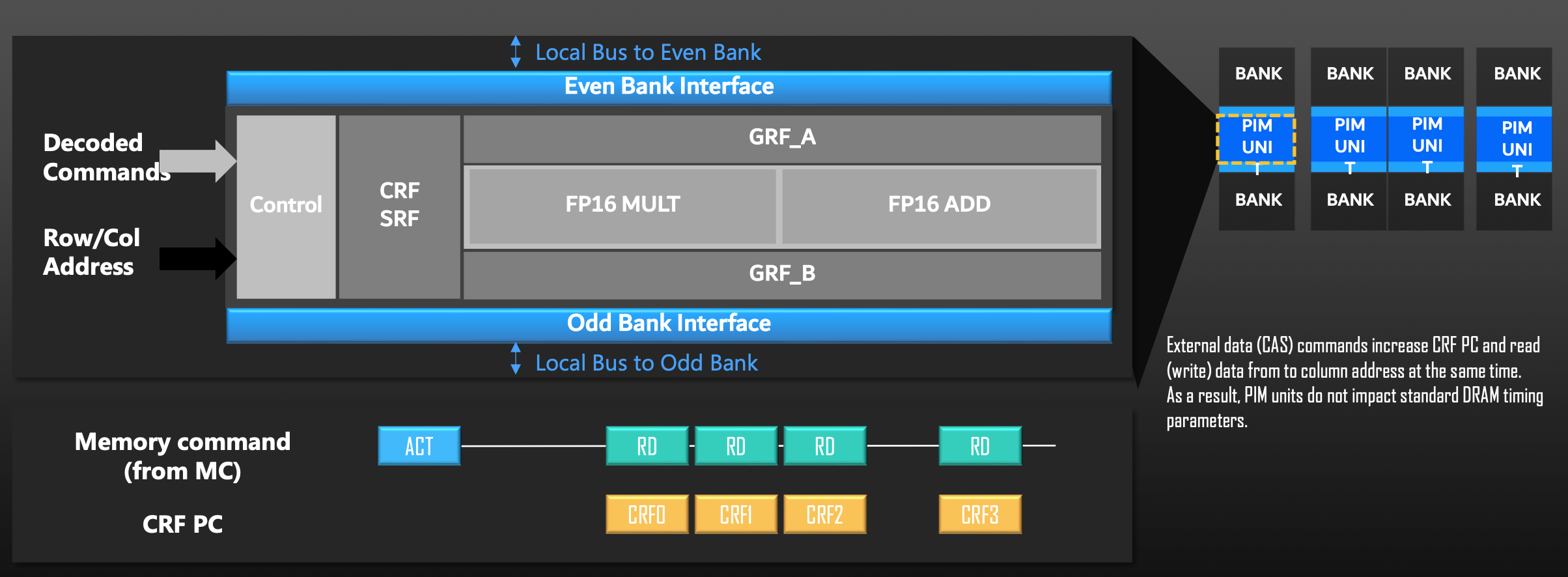

Samsung HBM2-PIM

Aquabolt-XL: Samsung HBM2-PIM with in-memory processing for ML accelerators and beyondCPU 핀 수나 PCB 배선을 늘려 메모리 대역폭을 물리적으로 확장하는 방식은 이미 물리적 한계에 도달했습니다. A

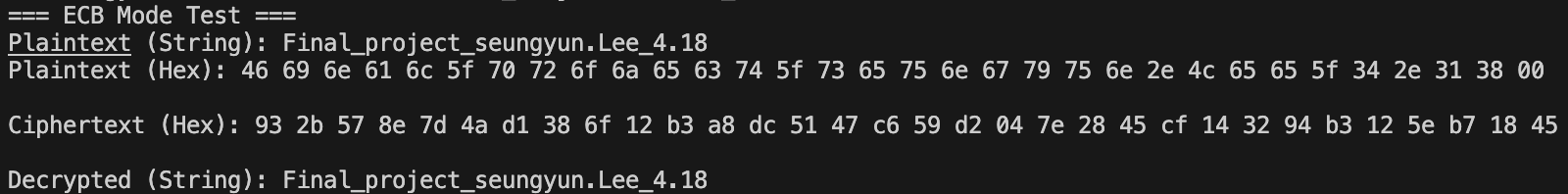

Cyber project

벤치마크 결과 분석 (보고서 작성용)1\. DES와 3DES의 선형적 속도 비례 (The 1:3 Ratio)10 MB 구간을 보면 DES 암호화는 약 107 ms, 3DES는 약 280 ms가 소요되었습니다. 3DES가 DES보다 정확히 2.5배에서 3배 정도 느린 것

HW4

$$n = p \\cdot q = 3 \\cdot 11 = 33$$$$\\phi(n) = (p - 1)(q - 1) = 2 \\cdot 10 = 20$$$$7 \\cdot e \\equiv 1 \\pmod{20}$$$7 \\cdot 3 = 21 \\equiv 1 \\p

Virtual Sequence, Sequencer

단일 Sequencer는 바이올린 연주자 한 명과 같습니다. 자기 악기(AXI 트랜잭션)만 연주할 줄 압니다.하지만 실제 칩에는 AXI 버스, APB 버스, I2C 통신, Interrupt 신호 등 수십 개의 에이전트(Agent)가 동시에 돌아갑니다.중앙 통제 (Cen